## Constraint programming for design space exploration of dataflow applications on multi-bus architectures

Amna Gharbi

#### ▶ To cite this version:

Amna Gharbi. Constraint programming for design space exploration of dataflow applications on multibus architectures. Hardware Architecture [cs.AR]. Institut Polytechnique de Paris, 2021. English. NNT: 2021IPPAT018 . tel-03515492

### HAL Id: tel-03515492 https://theses.hal.science/tel-03515492

Submitted on 6 Jan 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Constraint Programming for Design Space Exploration of Dataflow Applications on Multi-Bus Architectures

Thèse de doctorat de l'Institut Polytechnique de Paris préparée à Télécom Paris

École doctorale n°626 Institut Polytechnique de Paris (IPP) Spécialité de doctorat : Informatique

Thèse présentée et soutenue à Sophia Antipolis, le 10 Novembre, 2021, par

## Amna Gharbi

| Composition du Jury :                                                   |                       |

|-------------------------------------------------------------------------|-----------------------|

| Alix Munier-Kordon<br>Professeure, Sorbonne Université                  | Présidente            |

| Sebastien Voss<br>Professeur, FH Aachen, University of Applied Sciences | Rapporteur            |

| Alain Girault<br>Directeur de recherche, INRIA Grenoble                 | Rapporteur            |

| Frédéric Mallet<br>Professeur, Université Côte d'Azur                   | Examinateur           |

| Ludovic Apvrille<br>Professeur, Télécom Paris                           | Directeur de thèse    |

| Renaud Pacalet<br>Directeur d'étude, Télécom Paris                      | Co-directeur de thèse |

| Andrea Enrici<br>Ingénieur de recherche, Nokia Bell Labs France         | Co-encadrant de thèse |

de doctora ese

## Remerciements

« L'interdépendance est une valeur qui surpasse l'indépendance. »

#### Stephen R. Covey

Ce travail est le résultat de mes efforts mais c'est sans doute grâce au soutien et à l'accompagnement dont j'ai pu bénéficier que ce travail a vu le jour. C'est pour cela que je dédie les premiers mots de ce manuscrit à toutes ces personnes qui ont contribué à son aboutissement.

J'exprime toute ma reconnaissance à mes directeurs de thèse, Ludovic Apvrille et Renaud Pacalet, pour m'avoir accueilli au sein du labSoC. Ils m'ont fourni tout le soutien nécessaire pour réussir mon travail de recherche. Leurs conseils et leurs remarques précieuses sont pour beaucoup dans le résultat final de ce travail. Enfin, leurs nombreuses relectures et corrections de cette thèse ont été très appréciables.

Je remercie tout particulièrement Andrea Enrici de Nokia Bell Labs qui a toujours été disponible et s'est toujours intéressé à l'avancée de mes travaux. Ses encouragements m'ont aidé à persévérer dans les moments difficiles et ont gratifié les efforts que j'ai fournis tout au long de ma recherche.

Ensuite, je tiens à remercier tous les membres de mon jury pour le temps qu'ils ont consacré pour évaluer mon travail, ainsi que pour toutes les connaissances et l'expertise qu'ils ont apportées. Je remercie mes rapporteurs: Alain Girault et Sebastien Voss d'avoir pris le temps de lire ma thèse et de donner des remarques qui ont contribué à son amélioration, et les examinateurs : Alix Munier-Kordon et Frédéric Mallet pour l'intérêt qu'ils portent à ma recherche.

Un remerciement tout particulier va aux personnes qui ont égayé mes journées au labSoC. Merci à : Maysam, Matteo, Benjamin, Letitia, Minh et Le Van pour tous les moments que nous avons partagés. J'ai eu beaucoup de chance d'être entourée par vous pendant ces années. Merci à Rabéa pour toutes les informations utiles qu'elle n'a pas hésité à partager avec moi et les précieux conseils qu'elle m'a donnés. Merci à Tullio pour les discussions enrichissantes pendant les pauses-déjeuner. Ce travail n'aurait certainement pas vu le jour sans le soutien et les sacrifices immenses que mes parents, Najib et Malika, ont fourni. Leurs encouragements se sont inscrits dans ma tête et ont résonné à chaque épreuve que j'ai pu traverser me donnant force et détermination pour atteindre mes objectifs. Ils m'ont toujours poussé à apprendre et étaient le flambeau qui illuminait mon chemin. Merci maman et papa. Merci à mon frère, Ahmed, de m'avoir toujours diffusé un rayon de joie et de bonne humeur.

Enfin, merci à mon partenaire et époux, Mohamed, pour son soutien inconditionnel et son enthousiasme contagieux. Merci de m'avoir donné tout le soutien et l'amour pour donner le meilleur de moi-même. Merci d'avoir été ma joie et ma source de motivation quand elles me manquaient.

## Résumé substantiel

Le travail de cette thèse s'inscrit dans le cadre d'une collaboration entre Télécom Paris et Nokia Bell Labs France. Dans ce contexte, nous nous intéressons aux systèmes de traitement du signal. Un système de traitement du signal peut être perçu comme un système qui reçoit un signal d'entrée, par exemple, une vidéo ou des images, y applique un certain traitement, et produit un signal de sortie. Dans les systèmes modernes de traitement du signal, plusieurs unités de calcul hétérogènes sont embarquées sur la même puce et exécutent les tâches des applications en parallèle et d'une manière distribuée. Dans ce contexte, l'infrastructure de communication devient un élément clé pour la distribution des tâches sur les différentes unités de calcul en assurant le transfert des données d'une unité à l'autre.

Pour exploiter pleinement les capacités potentielles d'une architecture multiprocesseur, les décisions sur comment allouer et ordonnancer les tâches sur les unités de calcul, ainsi que les transferts de données sur les ressources de communication doivent être prises en compte. Il existe plusieurs architectures de communication offrant différents avantages et limitations rendant chacune plus ou moins adaptée selon les différents cas d'utilisation. Les architectures de communication couramment utilisées incluent typiquement des bus partagés, ou des crossbars, ou ont recours à du multi-bus avec des topologies personnalisables telles que les architectures hiérarchiques, les topologies en anneau, ou encore les réseaux sur puce.

Bien qu'il existe de nombreux travaux visant à automatiser la synthèse d'une topologie optimale pour les architectures multi-bus, les travaux visant à identifier une allocation et un ordonnancement des tâches et des communications se concentrent majoritairement sur le bus partagé ou sur les réseaux sur puce. Dans cette thèse, nous proposons trois contributions pour combler cette lacune : 1) Une formulation « Satisfiability Modulo Theories » (SMT) qui permet d'explorer les décisions d'allocation et d'ordonnancement sur les architectures multi-bus pour l'optimisation de la latence ; Nous démontrons son applicabilité pour produire des solutions pour des applications connues. 2) Pour améliorer le passage à l'échelle de la recherche optimale de la première contribution, nous proposons une nouvelle technique pour élaguer l'espace des solutions devant être explorées. Notre évaluation démontre un gain sur le passage à l'échelle. Finalement, 3) la consommation d'énergie par

les communications sur bus est étudiée ; nous montrons comment optimiser la latence et la consommation conjointement. Nos évaluations montrent comment différents compromis entre latence et consommation d'énergie peuvent être étudiés. De plus, nous montrons comment nos contributions ont été intégrées à un outil de modélisation et de vérification particulièrement adapté à la conception des systèmes embarqués au niveau système (TTool).

Dans cette thèse, nous considérons les applications de flux de données représentées par des graphes de dépendances, où les nœuds représentent les tâches et les arcs représentent les communications (ou des dépendances de données). Pour les architectures, nous considérons des architectures avec des unités de calcul hétérogènes, par exemple, un CPU, un DSP ou encore un accélérateur matériel spécialisé en un type de traitement particulier. Les unités de calcul peuvent avoir un ou plusieurs cœurs d'exécution. Pour l'architecture de communication, nous considérons les architectures à base d'un ou plusieurs bus. Ces derniers peuvent être disposés selon diverses topologies, par exemple, linéairement, en arbre, en anneau, ou encore d'une manière ad-hoc.

Nous proposons dans la première contribution de cette thèse un modèle de contraintes qui permet d'identifier : 1) une allocation des tâches sur les unités de calcul, 2) une allocation des communications aux routes de bus et éventuellement de bridges, 3) un ordonnancement des tâches sur les unités de calcul, et 4) une allocation des slots temporels sur les bus aux communications concurrentes. Le modèle proposé peut être configuré pour prendre en compte des contraintes de deadline sur les applications étudiées, ou encore pour minimiser la latence.

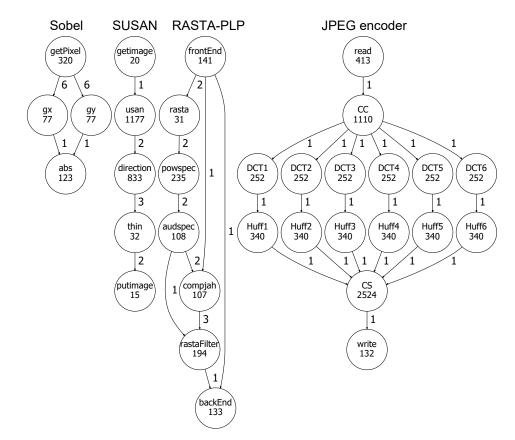

Pour évaluer la première contribution, nous avons sélectionné des applications de traitement de signal utilisées pour évaluer des travaux connexes, au même niveau d'abstraction. Ces applications sont : un filtre Sobel, un filtre SUSAN, une application RASTA-PLP, et un encodeur JPEG. Nous montrons que l'approche proposée permet d'analyser les décisions d'allocation et d'ordonnancement sur différentes topologies de bus pour l'optimisation de la latence. Nous montrons aussi qu'elle permet d'analyser les contentions sur les bus dues à la présence de plusieurs communications concurrentes. Cependant, les temps de calculs observés montrent une limitation majeure de l'approche vis à vis son passage à l'échelle.

Pour améliorer le passage à l'échelle de la recherche optimale de la première

contribution, nous proposons une nouvelle technique pour élaguer l'espace des solutions. Cette technique consiste à définir des limites temporelles pour les tâches et les communications. Ces limites sont pour une tâche : 1) le temps de début au plus tôt, 2) le temps de fin au plus tôt, 3) le temps de début au plus tard, et 4) le temps de fin au plus tard. Ainsi, lors de l'exploration de l'espace des solutions, uniquement les ordonnancements qui respectent ces limites temporelles sont étudiés.

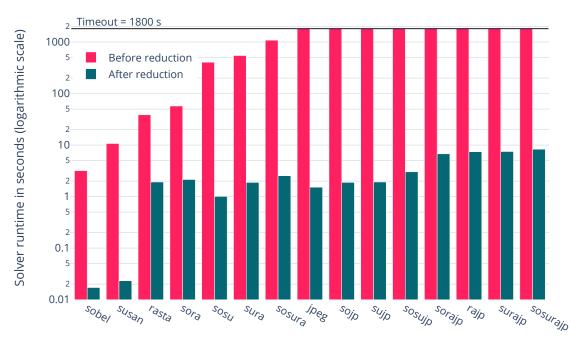

Nous comparons les temps de calcul obtenus avec la formulation initiale et ceux que nous obtenons après l'application de la technique de réduction. Nous montrons que nous obtenons une réduction significative des temps d'exécution d'au moins un ordre de grandeur.

Dans les deux premières contributions, nous nous sommes uniquement concentrés sur l'optimisation de la latence. Cependant, dans les systèmes du monde réel, il y a souvent plus d'un critère à satisfaire ou à optimiser, souvent en conflit l'un avec l'autre. Ainsi, dans la troisième contribution, nous étudions l'extension de notre approche pour tenir compte d'un deuxième critère. Comme dans cette thèse, nous nous intéressons aux architectures de communication multi-bus, nous considérons la consommation d'énergie par les communications comme deuxième critère. Nous proposons donc trois approches pour étudier conjointement l'optimisation de la latence et de la consommation.

La première approche peut être utilisée quand on recherche une solution qui minimise la latence en priorité et qui permet des réductions de la consommation mais pas au détriment de la latence. Pour cela, nous nous appuyons sur la méthode d'ordre lexicographique qui consiste à effectuer une première phase d'optimisation de latence, puis une deuxième phase de minimisation de la puissance sous la contrainte de latence minimale. Bien sûr, la deuxième phase n'a de sens que lorsqu'il existe plusieurs solutions minimisant la latence.

La deuxième approche permet d'obtenir des solutions minimisant la consommation tout en respectant des deadlines définis a priori. Pour ce faire, nous nous appuyons sur la méthode de la fonction objectif bornée qui minimise l'énergie sous une contrainte de latence.

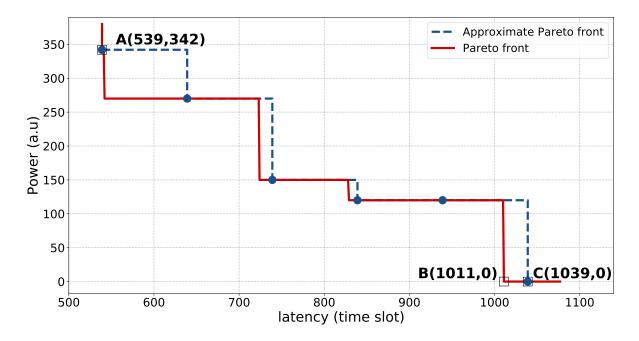

Finalement, la troisième approche vise à produire un ensemble de solutions optimales de Pareto en se basant sur une variante de la méthode dite « epsilonconstraint ». Dans cette approche, la solution la plus appropriée peut être sélectionnée parmi l'ensemble des solutions de Pareto généré.

Nous montrons que les trois approches permettent de générer différents compromis entre la latence et la consommation. Le passage à l'échelle de l'optimisation bi-critère représente la limitation majeure de la troisième contribution, surtout en ce qui concerne la troisième approche visant à générer un ensemble de solutions de Pareto.

Pour conclure, cette thèse s'intéresse aux architectures à base de bus mutiples. Pour ce type de plateformes, les contributions déjà proposées étaient insuffisantes. Le travail accompli dans le cadre de cette thèse comble cette lacune en permettant d'étudier les décisions d'allocation et d'ordonnancement dans ces architectures. La technique de réduction proposée apporte une amélioration significative des temps d'exécution. La troisième contribution démontre la flexibilité de l'approche proposée pour encoder différentes approches d'optimisation bi-critères et générer différentes solutions de Pareto.

Nous identifions deux axes principaux pour les perspectives de ce travail. Le premier axe porte sur l'extension de la formulation actuelle pour modéliser d'autres aspects des systèmes étudiés. Par exemple, la consommation d'énergie des unités de calcul ou encore la présence de mémoire partagée dans l'architecture. Le deuxième axe concerne l'élaboration de nouvelles techniques pour améliorer davantage le passage à l'échelle. Pour cela, nous discutons de quelques idées comme la décomposition temporelle et la rupture de symétrie.

# Contents

| Сс | onten | its      |                                  | 7  |

|----|-------|----------|----------------------------------|----|

| Li | st of | Figure   | S                                | 8  |

| Li | st of | Tables   |                                  | 9  |

| 1  | Intro | oductio  | on                               | 13 |

|    | 1.1   | Conte    | xt                               | 13 |

|    |       | 1.1.1    | Design Space Exploration         | 13 |

|    |       | 1.1.2    | Applications                     | 15 |

|    |       | 1.1.3    | Architectures                    | 16 |

|    |       | 1.1.4    | The segmented bus interconnect   | 18 |

|    | 1.2   | Proble   | em Statement                     | 19 |

|    | 1.3   | Contri   | bution                           | 20 |

|    | 1.4   |          | s Outline                        | 23 |

| 2  | Con   | itext an | nd Related Work                  | 25 |

|    | 2.1   | Desigi   | n Space Exploration Problems     | 26 |

|    |       | 2.1.1    | Application model                | 26 |

|    |       | 2.1.2    | Processing models: heterogeneity | 27 |

|    |       | 2.1.3    | Communication models             | 28 |

|    |       | 2.1.4    | Design decisions                 | 30 |

|    |       | 2.1.5    | Design objectives                | 31 |

|    |       | 2.1.6    | Mapping and scheduling models    | 33 |

|    | 2.2   | Desigi   | n Space Exploration Techniques   | 34 |

|   |      | 2.2.1 Evaluation methods                                                 | 35 |

|---|------|--------------------------------------------------------------------------|----|

|   |      | 2.2.2 Search strategies                                                  | 35 |

|   | 2.3  | Targeted Systems                                                         | 39 |

|   | 2.4  | Existing Design Space Exploration Work                                   | 40 |

|   | 2.5  | Summary and Conclusion                                                   | 48 |

| 3 | A Sa | atisfiability Modulo Theories Formulation for the Design Space Ex-       |    |

|   | plor | ration (DSE) of Multi-Bus architectures                                  | 53 |

|   | 3.1  |                                                                          | 53 |

|   | 3.2  | Problem definition                                                       | 55 |

|   | 3.3  | Workload Model                                                           | 55 |

|   | 3.4  | Architecture Model                                                       | 57 |

|   | 3.5  | Deployment Solution                                                      | 59 |

|   | 3.6  | The SMT formulation                                                      | 63 |

|   |      | 3.6.1 Decision variables                                                 | 64 |

|   |      | 3.6.2 Constraints                                                        | 67 |

|   |      | 3.6.3 Latency design objectives                                          | 69 |

|   | 3.7  | Implementation                                                           | 71 |

|   |      | 3.7.1 Overview of the implemented solution                               | 71 |

|   |      | 3.7.2 Model-based design                                                 | 72 |

|   |      | 3.7.3 UML/SysML-to-SMT transformation                                    | 75 |

|   |      | 3.7.4 Model-based deployment solution                                    | 76 |

|   | 3.8  | Evaluation                                                               | 76 |

|   |      | 3.8.1 Experiment 1: Best interconnect selection                          | 77 |

|   |      | 3.8.2 Experiment 2: Scalability evaluation                               | 82 |

|   | 3.9  | Summary and limitations                                                  | 85 |

| 4 | A R  | eduction Method to Prune the Design Space for the Problem of             |    |

|   | Sch  | eduling Tasks and Communications                                         | 87 |

|   | 4.1  |                                                                          | 87 |

|   | 4.2  | A Satisfiability Modulo Theories (SMT) Model for the Problem of Schedul- |    |

|   |      | ing Tasks and Communications                                             | 88 |

|   |      | 4.2.1 Assumptions                                                        | 90 |

|   |      | 4.2.2 The SMT Model                                                      | 90 |

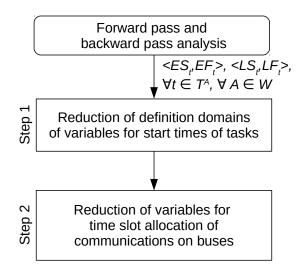

|   | 4.3  | Descr  | iption of the Design Space Reduction Method                     | 91   |

|---|------|--------|-----------------------------------------------------------------|------|

|   |      | 4.3.1  | Overview                                                        | 91   |

|   |      | 4.3.2  | The pre-analysis                                                | 93   |

|   |      | 4.3.3  | The reductions                                                  | 95   |

|   |      | 4.3.4  | Example                                                         | 96   |

|   | 4.4  | Evalua | ation                                                           | 97   |

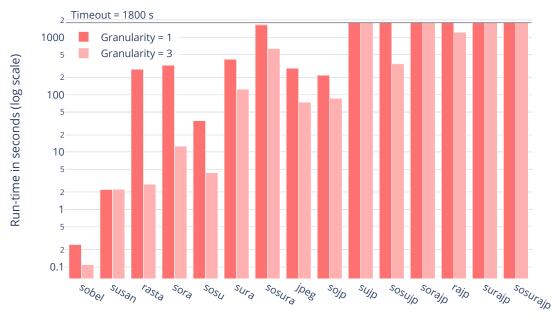

|   |      | 4.4.1  | Experiment 1: Influence on exploration run-time                 | 99   |

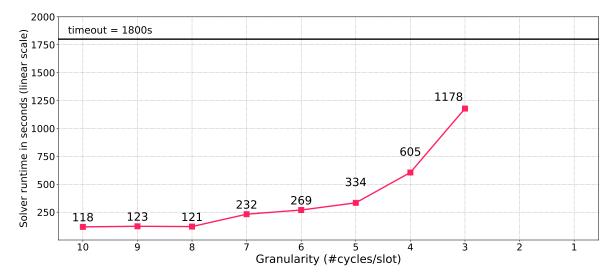

|   |      | 4.4.2  | Experiment 2: Influence on granularity                          | 102  |

|   |      | 4.4.3  | Experiment 3: Optimal solution search                           | 103  |

|   |      | 4.4.4  | Experiment 4: Adjusting granularity to solve larger scale prob- |      |

|   |      |        | lems                                                            | 105  |

|   | 4.5  | Concl  | usion                                                           | 109  |

| 5 | Exte | ending | the Latency SMT Model with a Power Consumption Model            |      |

|   |      | _      | us Interconnects                                                | 113  |

|   | 5.1  | Introd | uction                                                          | 113  |

|   | 5.2  | Power  | Consumption Modeling for the Multi-Bus Interconnect             | 116  |

|   |      | 5.2.1  | Scope and assumptions                                           | 116  |

|   |      | 5.2.2  | The SMT model                                                   | 117  |

|   | 5.3  | DSE f  | or Latency and Power Optimization                               | 119  |

|   |      | 5.3.1  | Approach 1: Minimize power under minimal latency                | 119  |

|   |      | 5.3.2  | Approach 2: Minimize power under deadline constraints           | 120  |

|   |      | 5.3.3  | Approach 3: Pareto optimality for latency and power consumptio  | n121 |

|   | 5.4  | Evalua | ation                                                           | 122  |

|   |      | 5.4.1  | Experiment 1: Evaluation of Approach 1 and Approach 2           | 122  |

|   |      | 5.4.2  | Experiment 2: Generating Pareto optimal solutions using Ap-     |      |

|   |      |        | proach 3                                                        | 125  |

|   |      | 5.4.3  | Experiment 3: Evaluating granularity effect                     | 128  |

|   | 5.5  | Concl  | usion                                                           | 132  |

| 6 | Con  | clusio | n and Future Work                                               | 135  |

|   | 6.1  | Summ   | nary of the contributions                                       | 135  |

|   |      | 6.1.1  | -                                                               |      |

|   |      | 6.1.2  | -                                                               |      |

|   |      |        |                                                                 |      |

|         | 6.1.3  | Summary of the third contribution                             | 137 |

|---------|--------|---------------------------------------------------------------|-----|

|         | 6.1.4  | Summary of the integration to a Model-Driven Engineering (MDE | )   |

|         |        | design environment                                            | 137 |

| 6.2     | Concl  | usions                                                        | 138 |

| 6.3     | Limita | tions and Improvements                                        | 138 |

| 6.4     | Future | e work                                                        | 139 |

|         | 6.4.1  | Extending the approach with new specification                 | 139 |

|         | 6.4.2  | Refining the pre-analysis with task mapping information       | 140 |

|         | 6.4.3  | Symmetry breaking in time slots allocation                    | 141 |

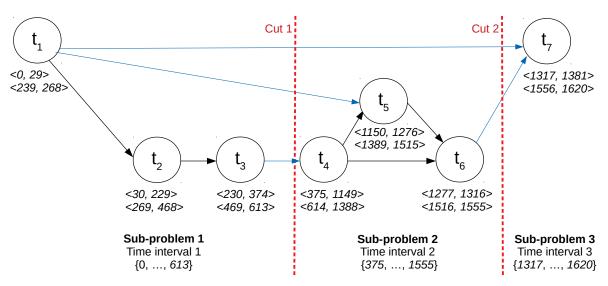

|         | 6.4.4  | Temporal decomposition                                        | 143 |

| Bibliog | raphy  |                                                               | 145 |

# **List of Figures**

| 1.1 | The Y-chart approach for DSE [36]                                                                                                                                                 | 14 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

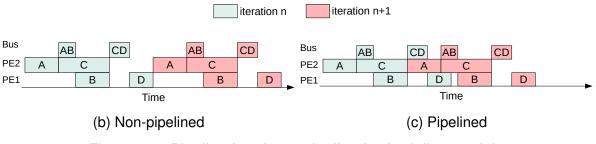

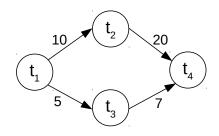

| 1.2 | Example of dataflow application dependency graphs [50]. Nodes repre-<br>sent tasks. Edges represent communications between them, annotated<br>with the amount of data to exchange | 16 |

| 1.3 | An example of a segmented bus communication architecture                                                                                                                          | 18 |

| 1.4 | An optimized design space exploration approach for the mapping and scheduling of tasks and communications on multi-bus architectures                                              | 22 |

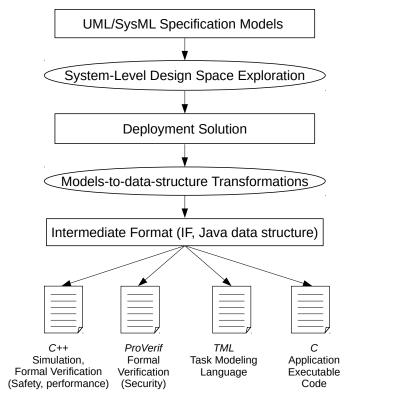

| 1.5 | The software architecture of TTool for the Unified Modeling Language (UML)/Systems Modeling Language (SysML) profile DIPLODOCUS                                                   | 23 |

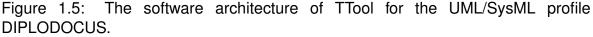

| 2.1 | Pipelined and non-pipelined scheduling models                                                                                                                                     | 34 |

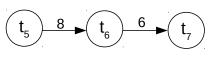

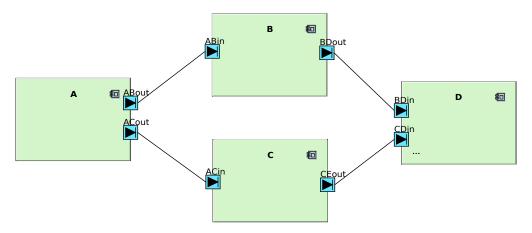

| 3.1 | Examples of applications' Directed Acyclic Graphs (DAGs). Vertexes rep-                                                                                                           |    |

|     | resent tasks, edges represent data dependencies annotated with the amount                                                                                                         | t  |

|     | of exchanged data                                                                                                                                                                 | 57 |

| 3.2 | Communication mapping scenarios.                                                                                                                                                  | 59 |

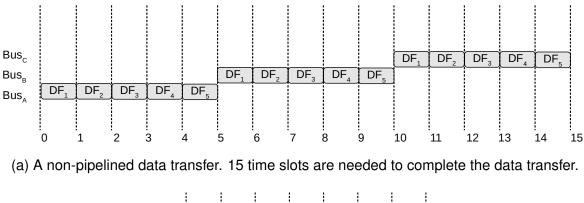

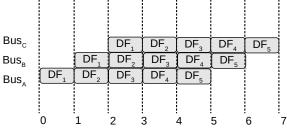

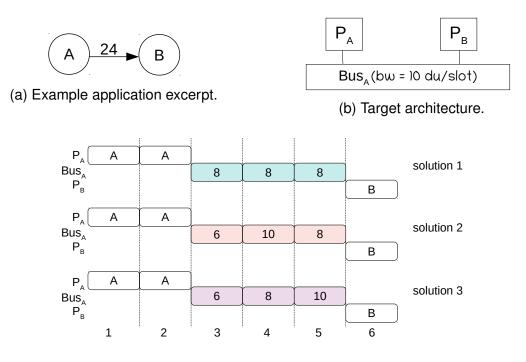

| 3.3 | A data transfer where 5 data fragments ( $DF_k, k \in \{15\}$ ) are transferred<br>on a route of 3 buses, $Bus_A$ , $Bus_B$ and $Bus_C$ in order                                  | 61 |

| 3.4 | An example showing communications scheduling on a route. A communi-<br>cation on a bus between two tasks X and Y during a slot is denoted XY,N                                    |    |

|     | where N is the size of the data fragment in arbitrary data units $(du)$                                                                                                           | 63 |

| 3.5 | The mapping of a task t to a Processing Unit (PU) $p$ and in particular to a Processing Element (PE) $c \in p$ , denoted by decision variables $x_{t,p}$ and                      |    |

|     | $z_{t,c}$ respectively.                                                                                                                                                           | 66 |

| 3.6   | Overview of the design space exploration workflow. The explanation of                                          |       |

|-------|----------------------------------------------------------------------------------------------------------------|-------|

|       | the pre-analysis sub-module will be given in Chapter 4                                                         | 72    |

| 3.7   | A SysML Block Diagram of an application model in TTool/DIPLODOCUS.                                             |       |

|       | Blocks represent tasks while links between blocks represent data depen-                                        |       |

|       | dencies                                                                                                        | 73    |

| 3.8   | Parameters of task D from Figure 3.7.                                                                          | 73    |

| 3.9   | UML activity diagram of task B from Figure 3.7.                                                                | 74    |

| 3.10  | A UML Deployment diagram of an architecture model in TTool/DIPLODOCUS                                          | S. 75 |

| 3.11  | The dependency graphs of our testbench. Edges are labeled with the                                             |       |

|       | number of exchanged data packets. Tasks are labeled with their execution                                       |       |

|       | times                                                                                                          | 77    |

| 3.12  | Common block diagram of Architecture 2 and Architecture 3                                                      | 78    |

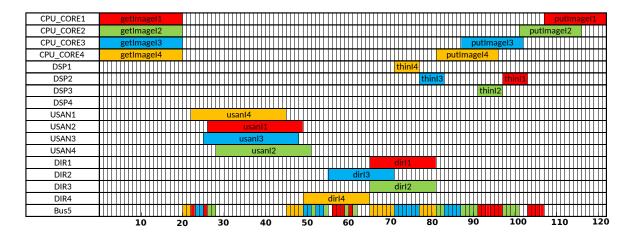

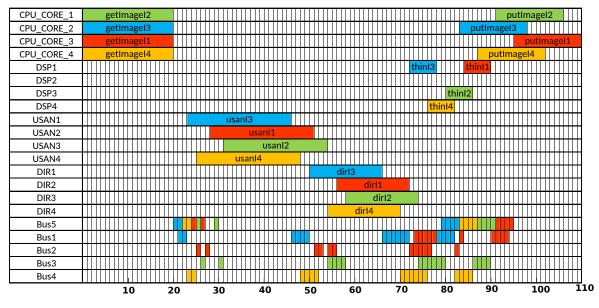

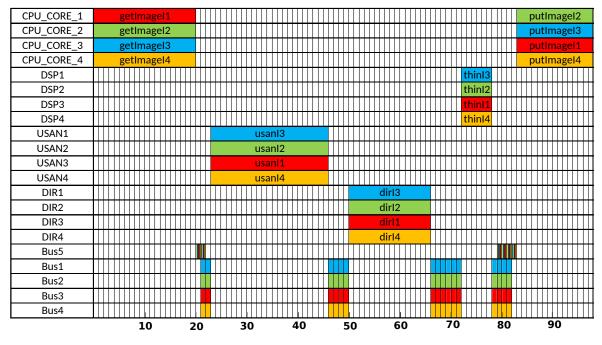

| 3.13  | Gantt chart for the solution found for <i>Architecture 1</i> (1 cell = 1 slot)                                 | 79    |

| 3.14  | Gantt chart for the solution found for Architecture 2 (1 cell = 1 slot)                                        | 80    |

| 3.15  | Gantt chart for the solution found for Architecture 3 (1 cell = 1 slot)                                        | 81    |

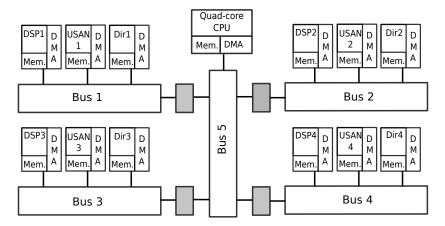

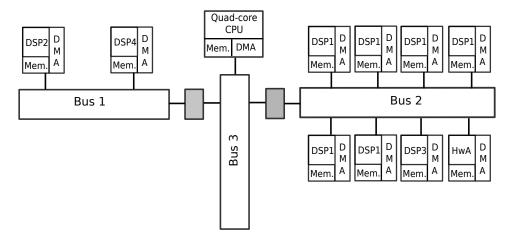

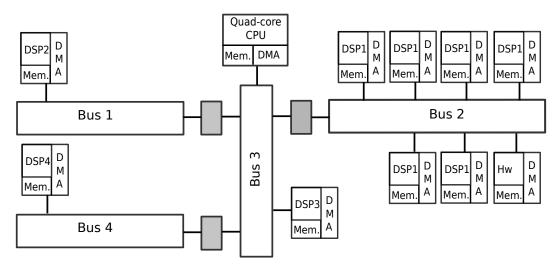

| 3.16  | Block diagram of Architecture A. Specialized Digital Signal Processors                                         |       |

|       | (DSPs) and the hardware accelerator are associated with the following                                          |       |

|       | operation sets: $O_{DSP1} = \{Huff, DCT\}, O_{DSP2} = \{pows, comp, filter\},\$                                |       |

|       | $O_{DSP3} = \{gx, gy\}, O_{DSP4} = \{USAN\} \text{ and } O_{HwA} = \{CS\}.$ Bus 3 has a                        |       |

|       | bandwidth of 64 <i>du</i> /slot and Bus 1 and Bus 2 have each a bandwidth of                                   |       |

| - · - | 32 <i>du</i> /slot                                                                                             | 83    |

| 3.17  | Solver run-time to produce a deadline-aware solution, as a function of                                         | 0.4   |

| 0.40  | different workloads, such that granularity is set to 1 slot = 1 cycle                                          | 84    |

| 3.18  | Solver run-time to produce a deadline-aware solution, as a function of                                         | 05    |

|       | exploration granularity for workload <i>sosurajp</i>                                                           | 85    |

| 4.1   | An optimized DSE approach for the mapping and scheduling of tasks and                                          |       |

|       | communications.                                                                                                | 89    |

| 4.2   | An overview of the reduction method.                                                                           | 92    |

| 4.3   | A task from the DAG annotated with temporal boundaries.                                                        | 94    |

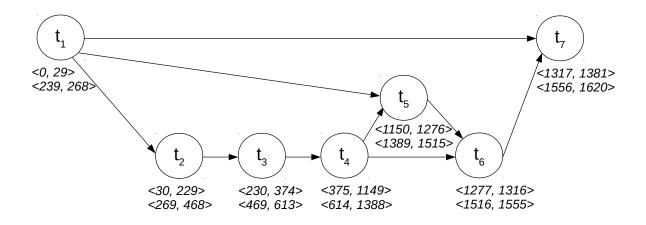

| 4.4   | An example of an application A where each task $t \in T^A$ is annotated with                                   |       |

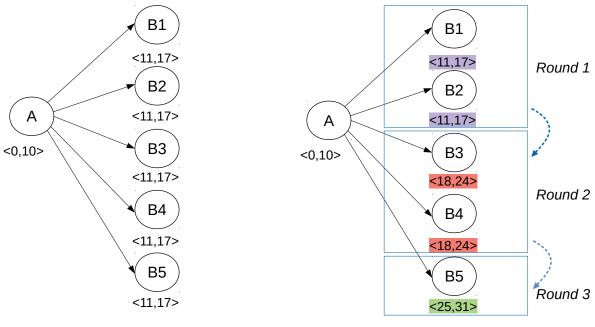

|       | the tuples $\langle ES_t, EF_t \rangle$ (top annotation) and $\langle LS_t, LF_t \rangle$ (bottom annotation). | 96    |

| 4.5  | Solver run-time to produce a deadline-aware solution, as a function of different workloads using initial formulation and optimized formulation, 1 slot = 1 cycle.                                                                  | 99  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

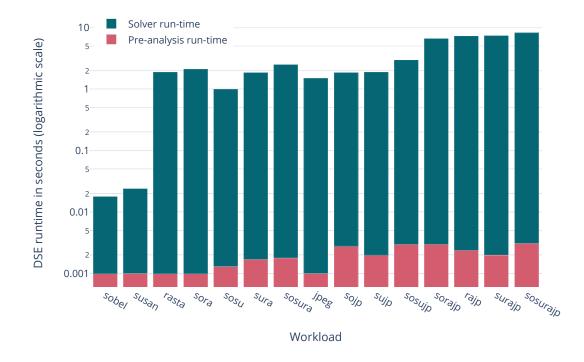

| 4.6  | Pre-analysis run-time against the solver run-time to produce a deadline-<br>aware solution, as a function of different workloads using optimized for-<br>mulation.                                                                 | 100 |

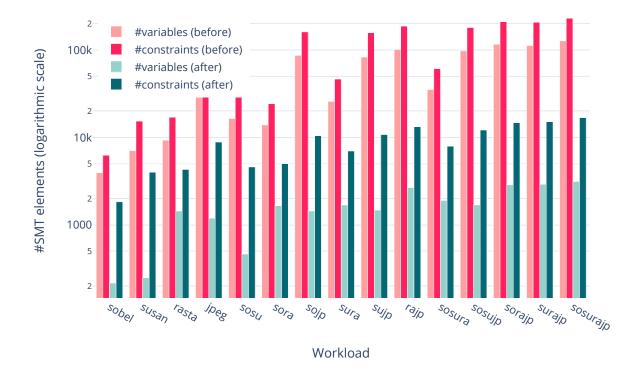

| 4.7  | Comparison of the size of the SMT model, as the number of created vari-<br>ables and constraints, before and after applying the reduction method, as<br>a function of different workloads                                          | 101 |

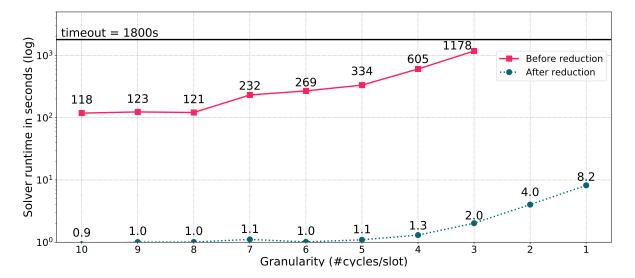

| 4.8  | Solver run-time to produce a deadline-aware solution, as a function of exploration granularity using initial formulation and optimized formulation for workload <i>sosurajp</i> .                                                  | 102 |

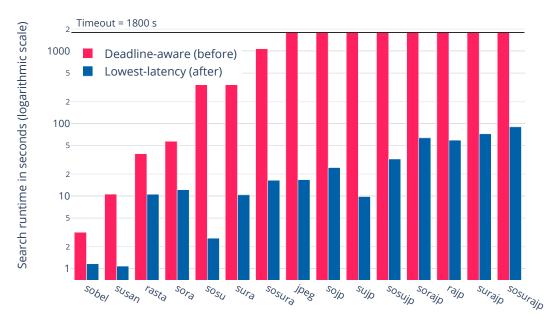

| 4.9  | Search run-time to produce an optimal solution using the optimized formu-<br>lation and a complementary Binary Search (BS), against run-time values<br>to find a first deadline-aware solution using the initial formulation, as a |     |

|      | function of different workloads.                                                                                                                                                                                                   |     |

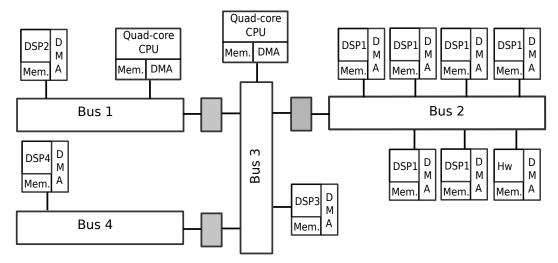

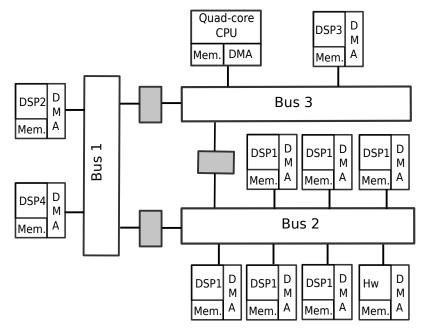

|      | Block diagram of Architecture B used in Experiment 4                                                                                                                                                                               |     |

|      | Block diagram of Architecture C used in Experiment 4                                                                                                                                                                               |     |

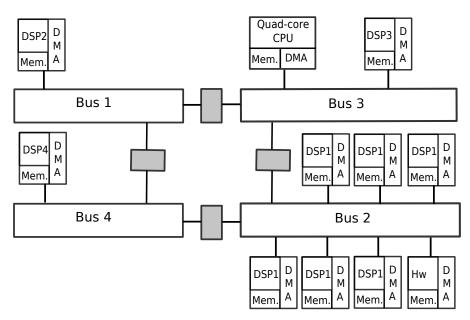

|      | Block diagram of Architecture D used in Experiment 4                                                                                                                                                                               |     |

| 4.13 | Block diagram of Architecture E used in Experiment 4                                                                                                                                                                               | 107 |

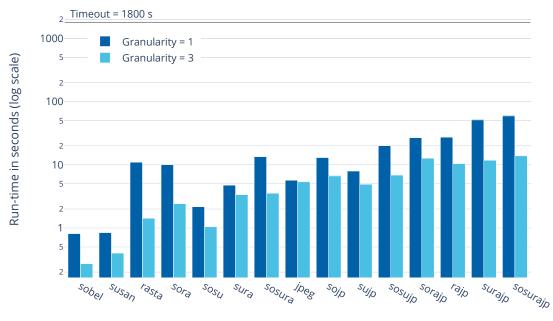

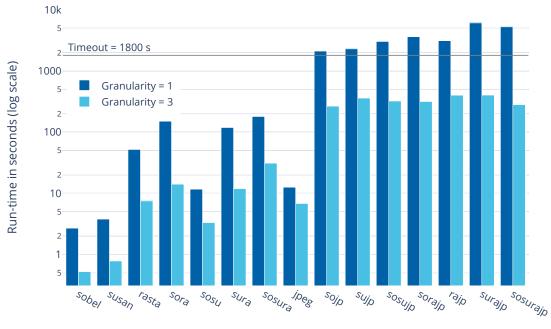

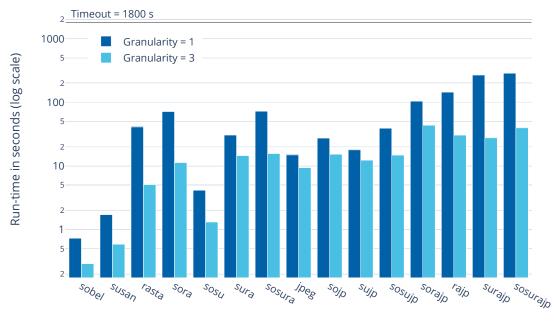

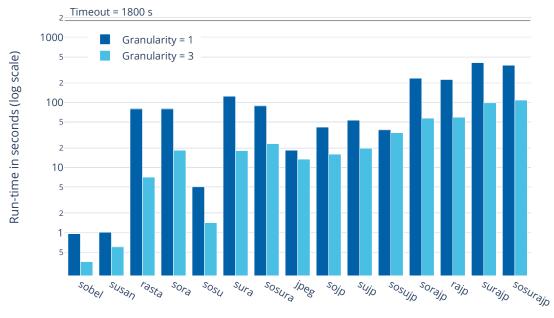

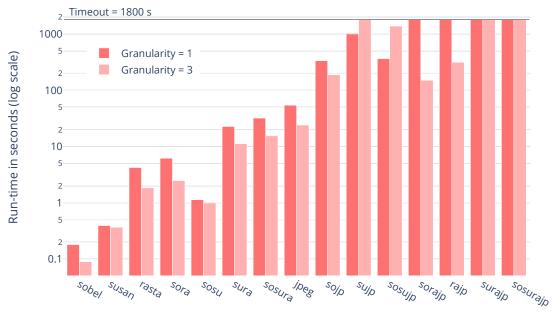

| 4.14 | Run-time to search the minimal latency solution on Architecture B using two levels of granularity (1 and 3), as a function of different workloads                                                                                  | 108 |

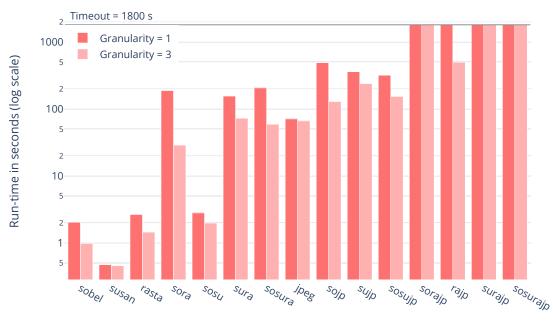

| 4.15 | Run-time to search the minimal latency solution on Architecture C using two levels of granularity (1 and 3), as a function of different workloads                                                                                  | 109 |

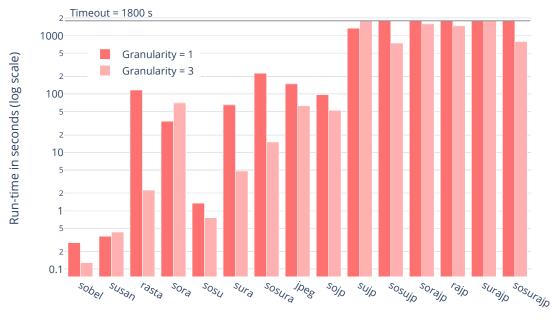

| 4.16 | Run-time to search the minimal latency solution on Architecture D using two levels of granularity (1 and 3), as a function of different workloads                                                                                  | 111 |

| 4.17 | Run-time to search the minimal latency solution on Architecture E using                                                                                                                                                            |     |

|      | two levels of granularity (1 and 3), as a function of different workloads                                                                                                                                                          | 112 |

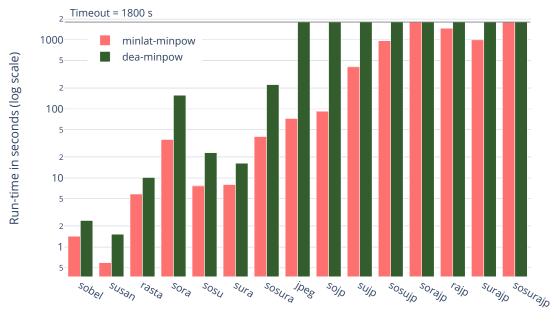

| 5.1  | Run-time to search the minimal power consumption: 1) under deadlines constraints ( <i>dea-minpow</i> ), 2) under minimum latencies ( <i>minlat-minpow</i> ), on Architecture A, as a function of different workloads.              | 123 |

| 5.2 | (Blue dashed staircase) Approximate Pareto front and (solid red stair-                        |     |

|-----|-----------------------------------------------------------------------------------------------|-----|

|     | case) actual Pareto front found using Approach 3                                              | 125 |

| 5.3 | Run-time to search the minimal power consumption under minimum la-                            |     |

|     | tencies on Architecture B, using two levels of granularity (1 and 3), as a                    |     |

|     | function of different workloads.                                                              | 128 |

| 5.4 | Run-time to search the minimal power consumption under minimum la-                            |     |

|     | tencies on Architecture C, using two levels of granularity (1 and 3), as a                    |     |

|     | function of different workloads.                                                              | 129 |

| 5.5 | Run-time to search the minimal power consumption under minimum la-                            |     |

|     | tencies on Architecture D, using two levels of granularity (1 and 3), as a                    |     |

|     | function of different workloads.                                                              | 131 |

| 5.6 | Run-time to search the minimal power consumption under minimum la-                            |     |

|     | tencies on Architecture E, using two levels of granularity (1 and 3), as a                    |     |

|     | function of different workloads.                                                              | 132 |

| 6.1 | Excerpt of an application graph where each task $t$ is annotated with the                     |     |

|     | tuple of earliest start and finish times $\langle ES_t, EF_t \rangle$ . Task A has a duration |     |

|     | of 11 time slots. Tasks $Bi, i \in \{1 \dots 5\}$ have each a duration of 7 time slots        | 141 |

| 6.2 | Example of symmetric solutions in slot allocation.                                            |     |

| 6.3 | Example illustrating time decomposition of the DSE problem.                                   | 144 |

# **List of Tables**

| A summary of selected related work                                                                                                                                                                  | 48                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Notations for the SMT formulation                                                                                                                                                                   | 65                                                                                                                                                                                                                                                                                                                                                                                                   |

| Examples of the reductions applied on application $A$ from Figure 4.4 Optimality gap (%) and speed-up factor of solutions found at granularity =                                                    | 97                                                                                                                                                                                                                                                                                                                                                                                                   |

| Interconnect power reduction percentage and approximate overall power reduction for all workloads, on Architecture A, for <i>dea-minpow</i> and <i>minlat-minpow</i> .                              | 124                                                                                                                                                                                                                                                                                                                                                                                                  |

| Quality gap (%) and speed-up (positive values) or slow-down (negative values) factor of solutions found at granularity = 3, compared to solutions found at granularity = 1, for a set of workloads. | 130                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                     | Examples of the reductions applied on application <i>A</i> from Figure 4.4 Optimality gap (%) and speed-up factor of solutions found at granularity = 3, compared to solutions found at granularity = 1, for a set of workloads Interconnect power reduction percentage and approximate overall power reduction for all workloads, on Architecture A, for <i>dea-minpow</i> and <i>minlat-minpow</i> |

# Glossary

- **CP** Constraint Programming. 39, 40, 43–45, 100

- CPU Central Processing Unit. 22, 31, 42, 54, 62, 71, 72, 74, 91

- **DAG** Directed Acyclic Graph. 7, 52, 53, 60, 81, 85

- **DMA** Direct Memory Access. 6, 31, 41, 54–56

- **DSE** Design Space Exploration. 3, 8, 19–21, 35–37, 39, 40, 44, 47–49, 59, 65, 69, 73–75, 79, 80, 91, 92, 94–97, 99

- **DSP** Digital Signal Processor. 13, 22, 62, 71, 72, 74, 91

- FFT Fast Fourier Transform. 53

- FPGA Field Programmable Gate Array. 13, 22, 28, 31, 42, 47

- GPU Graphics Processing Unit. 22

- HSDF Homogeneous Synchronous Data-Flow. 40, 42

- ILP Integer Linear Programming. 38, 40, 41, 43–45, 100

- LP Linear Programming. 38, 39

- MILP Mixed-Integer Linear Programming. 38, 42, 45

- MPSoC Multi-Processor System on a Chip. 13, 15, 20, 22, 74, 91

- NoC Network on a Chip. 14, 22, 47, 80, 81

- PE Processing Element. 53-56, 60-63

- **PU** Processing Unit. 54–56, 60, 62

- RTL Register Transfer Level. 15, 17

- SAT Boolean Satisfiability Problem. 30, 39, 40, 42, 45

- **SDF** Synchronous Data Flow. 36, 37, 40–43

- **SMT** Satisfiability Modulo Theories. 3, 4, 8, 9, 26, 28, 30, 34, 39–41, 43–45, 47, 48, 59, 60, 65, 68, 69, 76, 79–81, 88, 92, 94, 96, 97, 99, 100

- SysML Systems Modeling Language. 3, 6, 7, 26, 27, 65, 66, 68, 69

- UML Unified Modeling Language. 3, 6, 7, 26, 27, 65–69

## **Chapter 1**

# Introduction

## 1.1 Context

The work of this thesis is part of a collaboration between Télécom Paris and Nokia Bell Labs France. In this context, we focus on the system-level Design Space Exploration (DSE) of embedded systems for the execution of signal processing applications. We focus on multi-bus architectures that are well-suited for the deployment of signal processing applications. In this Section, we will first define the scope and aim of the DSE in this thesis, in subsection 1.1.1. Then, we will define the target applications and architectures respectively in subsections 1.1.2 and 1.1.3.

#### 1.1.1 Design Space Exploration

In the systems we target, a DSE process aims at identifying the mapping and scheduling of both application tasks and communications between these tasks, such that design constraints and objectives are met. *Design constraints* refer to the set of requirements that are inherent to application and architecture definitions, and that mapping and scheduling decisions should respect. Basically, design constraints concern the application constraints (e.g., precedence constraints between tasks) and capacities of the architecture (e.g., memory capacity, connectivity scheme). *Design objectives* refer to performance goals, that are, for a given system metric, the proposed solution should either be below or over a given threshold (*Satisfy*), or optimal (*Min*- *imize/Maximize*). Examples are minimizing latency, satisfying real-time deadlines, minimizing power consumption or maximizing throughput. DSE analyzes different alternatives of mapping and scheduling, and selects for deployment the decisions which are compliant with design constraints, and satisfy best design objectives. This decision-making is a key step in embedded systems design [41] but is also complex and time-consuming [30, 53]. In fact, the majority of DSE problems (e.g., scheduling problems) for a multiprocessor architecture are NP-hard [25, 59].

One way to deal with the complexity of embedded systems design is to raise the level of abstraction from which the design is perceived to the so-called *systemlevel* [30]. Keutzer et al. [34] suggest that design decisions must be taken at the highest level of abstraction to allow exploiting all the degrees of freedom that are available. In fact, high-level abstractions allow global design methodologies by omitting precise circuit behavior details [30]. The work of this thesis, as well as the discussions in this manuscript, are located at the system-level of abstraction.

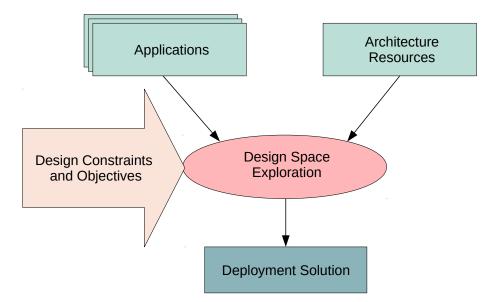

Figure 1.1: The Y-chart approach for DSE [36].

DSE is typically supported by means of automatic or semi-automatic design tools and methods. DSE is often associated with the Y-chart approach [36], illustrated in Figure 1.1. The Y-Chart takes as input one or several applications and the available architecture resources, as well as design constraints and objectives. Subsequently, it relies on analysis and search techniques to navigate the design space and evaluate potential design candidates. Finally, it outputs a deployment solution that describes the decisions which were taken. In this thesis, a *deployment solution* refers to a *mapping* and a *scheduling* that we define as follows.

- Mapping is the spatial allocation of architecture resources (processing resource, communication resource) and their assignment to application parts (tasks, communications). A mapping concerns the association of tasks to processing resources as well as the mapping of communications to paths (routes) from the architecture.

- Scheduling is the temporal allocation of architecture resources to application parts. It refers to the scheduling of tasks on processing resources and the scheduling of data transfers between tasks on communication resources.

#### 1.1.2 Applications

The dataflow paradigm is a very good fit for signal processing applications [21]. A dataflow application consists of a set of processing steps (tasks)—which operate on data to transform it— related by data dependencies (communications), which aim at exchanging data between tasks. Mapping of communications should resolve how data transfers between the related tasks can be performed by architectural components. A dataflow application is specified by means of a dependency graph where nodes represent tasks and edges represent communications between them.

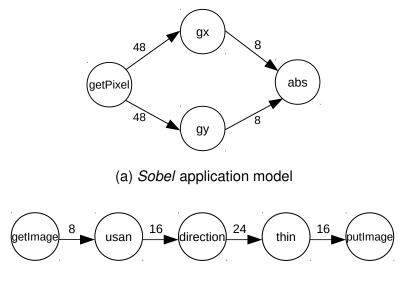

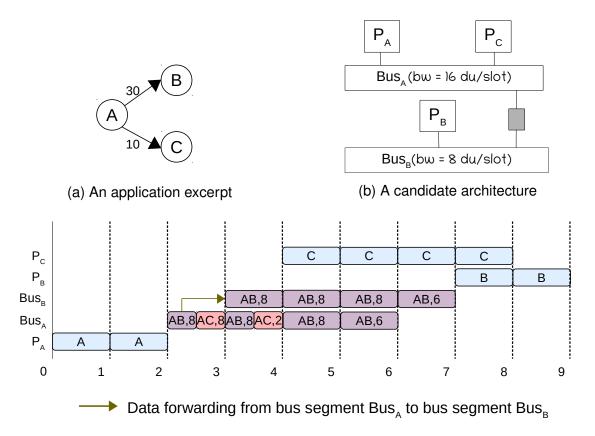

Examples of dataflow applications are *Sobel* and *SUSAN* filtering algorithms illustrated in Figure 1.2. *SUSAN* (Smallest Univalue Segment Assimilating Nucleus), Figure 1.2b, is a noise-reduction algorithm for edge and corner detection in images. It uses nonlinear filtering to reduce noise in an image while preserving its underlying structure [60]. Here, task *direction* produces data which is consumed by task *thin*: after task *direction* has determined the direction of an edge to decide whether or not a pixel is an edge point, a thinning algorithm (*thin*) is applied to the detected edges. *Sobel* is a filtering algorithm used to emphasize edges on an image. It performs a 2-D spatial gradient measurement on an image and emphasizes regions of high spatial frequency which correspond to edges. In a signal processing system, multiple applications, such as *Sobel* and *SUSAN*, can run in parallel and have their tasks and

(b) SUSAN application model

Figure 1.2: Example of dataflow application dependency graphs [50]. Nodes represent tasks. Edges represent communications between them, annotated with the amount of data to exchange.

communications compete to shared resources. Besides, applications are often subject to one or several design objectives. In case multiple applications are executed in parallel, different timing design objectives can be associated to each application to account for various levels of criticality. For instance, while the execution of an application A should end before a real-time deadline, the execution of an application B should be as short as possible.

#### 1.1.3 Architectures

A major evolution in embedded system design was enabled by the migration from the single processing paradigm to parallelization [79]. Multi-Processor Systems on a Chip (MPSoCs) were developed to parallelize calculations on multiple processing resources in order to meet design objectives in the areas of communications, signal processing, multimedia, networking [78, 79]... To reach the design objectives of applications, MPSoC architectures tend to be heterogeneous such that various types of processing resources (e.g., Digital Signal Processor (DSP), general-purpose Central Processing Unit (CPU), Graphics Processing Unit (GPU)) are integrated within a single chip and prompted to work in parallel on various applications calculations (tasks). In this context, communications, in the form of data exchanges between different processing resources, become crucial and represent a key enabler to distribute tasks over multiple processing resources.

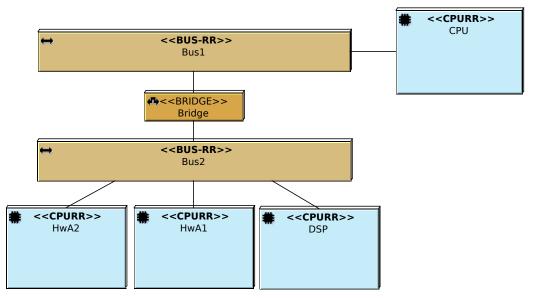

There is a range of communication architectures (also referred to as intercon*nect* in this thesis) that can be deployed in a MPSoC design, each offering a certain trade-off between design objectives [46], and thus are more or less adapted to the communication needs of a given application. For example, while Networks on a Chip (NoCs) scale better with the number of components connected, shared buses frequently have lower power consumptions and smaller area costs [45]. The shared bus is known as the simplest communication architecture. It consists of parallel wires to which all system components are connected. Only one component can transfer data on the shared bus at any given time. Consequently, increasing the number of components will lead to contentions and performance degradations, which translate to a poor scalability. Crossbar is a communication architecture with a set of buses operating in parallel. It can be partial (i.e., each component is connected to only a subset of the others) or full (i.e., each component is connected to all others) depending on the connectivity requirements. A NoC [7] consists of a network of routers and links where data is sent through the network in form of packets. The multi-bus (also referred to as the segmented bus in this manuscript) comes half way between the shared bus and the NoC. It is a bus-based communication architecture where the system bus is split into two or multiple segments (also called buses, or bus segments in this thesis). Each segment connects a subset of system components and operates in parallel to other segments. Different bandwidth capacities can be allocated to each bus segment, depending on the communication needs of components locally connected to the segment. For example, a hierarchical bus can be seen as a segmented bus for which some design restrictions on the structure and protocol have to be respected. In this thesis, we focus on multi-bus communication architectures which will be discussed further in the next Section.

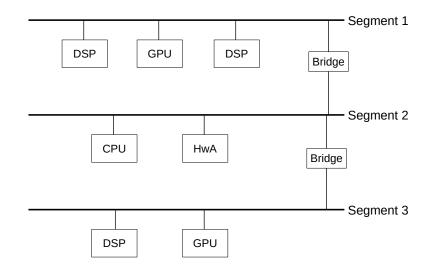

Figure 1.3: An example of a segmented bus communication architecture.

#### 1.1.4 The segmented bus interconnect

The segmented bus is a communication architecture that was first proposed in the late 90's [13] as an alternative to shared bus architectures (i.e., a single bus connecting all system components). These architectures suffer of scalability issues: as the number of connected components increases, the length of the bus wires and the load capacitances increase. In turn, this translates to longer signal propagation delays and to increased power consumption [46].

To overcome this limitation, the segmented bus proposes to split the system bus into segments such that each bus segment behaves as a normal bus, shared between a reduced set of local components. Each segment is allowed to operate in parallel to other segments and unused segments can be deactivated. Segmentation fosters parallel processing and communications, and reduces power consumption, as communications do not need to activate and utilize the entire bus system [81]. Figure 1.3 gives an example of an architecture with a three-bus segments communication architecture. Data can cross as many bus segments as needed to reach the intended destination. For instance, a data transfer between the GPU connected to Segment 1 and the DSP on Segment 3 activates all the bus segments. The inter-segment communications are governed by means of bridge components. A data transfer between the CPU and the hardware accelerator (HwA) connected to Segment 2 involves only the latter segment to be active. Segment 1 and Segment 3 remain inactive as long as none of their local components is involved in a data transfer.

Multi-bus interconnects are the preferred communication architecture in many designs (e.g., MPEG-4 decoder [73], Spiking Neural Network (SNN) [6]), thanks to improvements they offer in terms of latency, power consumption and area cost. In terms of performance characteristics, they can be positioned halfway between the simple but poorly scalable shared-bus architectures and the more complex NoCs.

In this thesis, we focus on multi-bus (segmented) communication architectures. We aim at providing methods and tools to allow investigating mapping and scheduling of dataflow applications (i.e., signal, image and video processing applications) that allow engineers to evaluate and compare the performance of bus-based interconnects with different topologies (e.g., shared, segmented)

### 1.2 Problem Statement

Designing a multi-bus architecture, even when the number and type of processing resources have been fixed, comes with a set of entangled issues that need to be solved. These issues include: how many bus segments to create? What is the bandwidth of each bus segment? How to connect segments to each other? Where to place processing resources as well as which tasks to map to these resources? How to map and schedule concurrent communications and avoid contentions? These issues are also typically subject to conflicting design objectives such as minimum latency and power consumption.

Ideally, during design, all these issues would be addressed in an integrated manner so that their inherent interdependencies could be analyzed, and globally optimal design decisions could be taken. However, in practice, a unified solving of all these issues may be prohibitively expensive. Thus, basically, design methodologies focus on solving several issues, separately, like finding an optimized topology and placement of processing resources [17, 55, 56], or address mapping and scheduling but restrict the number of buses to a unique bus [35, 39, 50, 51].

This lack in design methodologies for segmented bus architectures results into an under-utilization of their full potential. For instance, common designs typically segment buses in only two parts: high-speed and low-speed processing resources, while a larger spectrum of communication schemes could be explored and tailored to the application communication needs. Moreover, lacking systematic methodologies to study application communication needs (e.g., mapping and scheduling concurrent communications) on a target architecture usually leads to oversizing the interconnect bandwidth, that is, wasted cost and area.

In this thesis, we provide methods, techniques and tools for the design space exploration of segmented bus architectures with various topologies. We focus on topologies pre-defined by a user and leave the automation of topology synthesis for future work.

The contributions of this thesis target the following problems:

- How to efficiently map and schedule tasks and communications of multiple independent applications on a multi-bus architecture (example in Figure 1.3) such that design objectives on latency and power consumption are satisfied?

- What is the **minimum bandwidth required** on each bus under latency and power consumption design objectives?

### 1.3 Contribution

The work of this thesis consists in providing a Constraint Programming (CP)-based DSE approach for tasks and communications of dataflow applications. The proposed approach relies specifically on Satisfiability Modulo Theories (SMT). The aim of the proposed DSE is to find a mapping and scheduling of tasks and communications on an **existing, fixed, multi-bus architecture**. However, it can also be used to guide the **design of new architectures** (e.g., number of buses, interconnect topology), by comparing the found solutions for various architectures and selecting the architecture that best meets the design objectives. In the following, unless otherwise stated, we will use the terms **design** (and **DSE**), for both activities.

Communications between processing resources are allowed to traverse a single bus segment or as many bus segments as needed. If several routes are available between a pair of processing resources, the exploration procedure selects the route that best satisfies the design objectives. The aim of the proposed DSE is to provide a mapping and scheduling of tasks and communications such that design objectives on latency and power consumption of the multi-bus interconnect are met. A design objective on latency for a given application could be either to satisfy a deadline constraint, or to minimize latency. Multiple applications competing for shared resources can be examined and deployed simultaneously. Besides, we derive estimations on the minimum bandwidth required on each bus segment such that the latency design objective is met and the overall power consumption of buses is minimized. To improve the scalability, we propose a technique which aims at accelerating the joint solving of task and communication scheduling by pruning the temporal domains where variables for the scheduling of tasks and communications are defined. This allows to focus scheduling solutions on temporal domains, which are feasible with respect to precedence relationships and architecture capacities. The proposed technique brings a significant improvement to the DSE run-time.

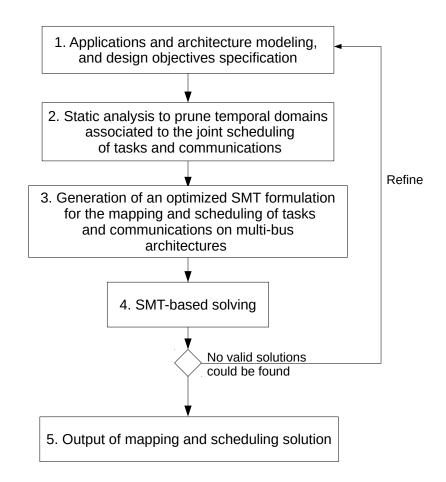

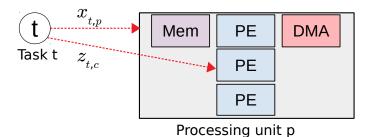

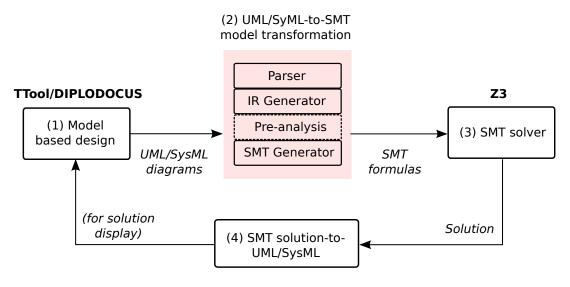

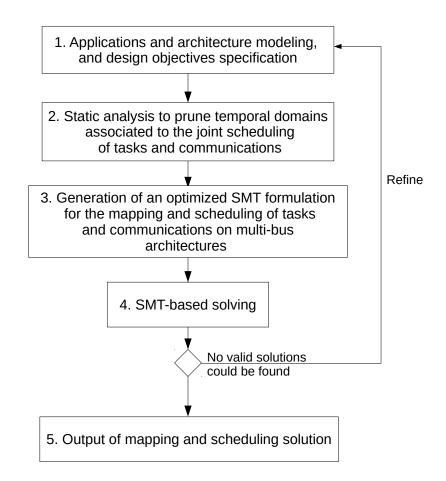

The steps of the proposed DSE approach are illustrated in Figure 1.4. Steps 2 and 3 denote our contributions. Once applications and architecture models are captured and design objectives are specified in Step 1, Step 2 performs an analysis of the input applications and architecture models to calculate *temporal boundaries* for tasks and communications. This step aims at reducing the run-time spent of Step 4. Step 3 translates input models, design objectives and constraints into a SMT model which describe the joint mapping and scheduling of tasks and communications. This SMT model is optimized thanks to the pre-analysis performed in Step 2. A state-of-the-art SMT solver is used to solve the formulation in Step 4 and return a mapping and scheduling solution if the formulas are satisfiable. If none of the candidates in the design space meets the design constraints and objectives, the user may need to refine the input specification. The output mapping and scheduling solution is optimized with respect to latency and power consumption of the interconnect.

We integrated our approach into a state-of-the-art design environment: TTool [2, 3]. TTool is a free and open-source UML/SysML framework supporting several UML profiles, including DIPLODOCUS [72] that targets hardware/software partitioning. TTool/DIPLODOCUS allows a user to model systems through UML/SysML diagrams and provides automated formal verification, transaction-based simulation and code generation for a given target hardware. However TTool/DIPLODOCUS lacks an engine to perform automatic DSE at system-level. We address this lack by the integra-

Figure 1.4: An optimized design space exploration approach for the mapping and scheduling of tasks and communications on multi-bus architectures.

tion of our contributions tightly within TTool/DIPLODOCUS.

Figure 1.5 illustrates the software architecture of TTool/DIPLODOCUS after the integration of our DSE. It takes input applications and architecture models with their properties as UML/SysML diagrams, performs system-level DSE according to the flow described in Figure 1.4, and outputs the deployment solution. The output solution can itself represent an input to further investigation at lower abstraction levels like transaction-based simulation. In Figure 1.5, a transformation to C++ code allows to perform simulations for the generated deployment solution.

### 1.4 Thesis Outline

The remainder of this thesis is organized as follows.

- In Chapter 2, we identify the components of a DSE approach at system-level and discuss the criteria that define and differentiate DSE problems and solving techniques. Then, we position our contribution according to these criteria and argue our choices. Finally, we review existing DSE works most closely related to ours and highlight the differences with respect to our work.

- Chapter 3 presents our SMT formulation for the DSE of architectures with a multi-bus interconnect. The proposed formulation captures joint tasks and communications mapping and scheduling and allows to analyze their interdependencies. We solve this formulation using a state-of-the-art SMT solver in order to propose a solution which satisfies deadlines or minimize latencies for

multiple applications. The Chapter also presents a case study that shows how the approach efficiently assists the designer in selecting the best interconnect topology for a given set of applications.

- In Chapter 4, our technique to prune the design space and accelerate the SMT solving step is introduced. The speed-up is evaluated for a benchmark of a set of real-world applications. Experiments demonstrate the efficiency of our technique to drastically reduce the DSE run-time.

- Chapter 5 presents our modeling of power consumption of the multi-bus interconnect which has two objectives: first assess the power consumed by buses in order to minimize it. Second, capture the bandwidth requirements of each bus in order to compute the minimum per-bus bandwidth required to achieve the design objectives on latency and power consumption.

- Chapter 6 concludes the manuscript and gives insights into future directions for the work accomplished in this thesis.

## Chapter 2

# **Context and Related Work**

In this thesis, we study the Design Space Exploration (DSE) of dataflow applications on architectures with a multi-bus interconnect, at Electronic System-Level (ESL) of abstraction. ESL is a design methodlogy that focuses on high abstraction level. It is defined in [5] as "the utilization of appropriate abstractions in order to increase comprehension about a system, and to enhance the probability of a successful implementation of functionality in a cost-effective manner, while meeting necessary constraints". In this chapter, we focus only on works at ESL of abstraction. The DSE problem consists in the decision problem of finding a mapping and a scheduling of tasks and communications with respect to some design objectives. To solve these problems, DSE techniques are needed. In this Chapter, we have identified two main classes of criteria to organize the related work. The first class concerns aspects that define the DSE problem to be solved, like the target architecture characteristicsand how these are accounted for during mapping and scheduling-or the design objectives to achieve (e.g., minimize latency, minimize power consumption). The second class refers to the techniques proposed to solve the DSE problem like the search strategies used to navigate the design space towards sought solutions. We will discuss these criteria in details in this chapter. Afterwards, we will position our work with respect to the targeted systems. Following that, we will discuss existing work and highlight why it is not suited to solve the problem we study in this thesis. Finally, we conclude and motivate the choices of our work.

The remainder of this Chapter is articulated in five Sections: Sections 2.1 and 2.2

define the criteria that we identified to classify DSE work: Section 2.1 discusses the different aspects and assumptions that define a DSE problem such as the design decisions, the target architecture model and the scheduling solution model. Section 2.2 explains the key components of a DSE approach (e.g., the search strategy) and different alternatives for each component. Section 2.3 positions and motivates our contribution with regard to the criteria discussed in Sections 2.1 and 2.2. In Section 2.4, we review existing DSE work most closely related to our work. Finally, Section 2.5 concludes this chapter and gives an overview of the contributions of this thesis, their motivations, and how our work is different from the existing literature.

### 2.1 Design Space Exploration Problems

#### 2.1.1 Application model

In this Section, we discuss the Model of Computation (MoC) used to capture applications. A MoC describes the set of rules that govern the execution of an application, by defining the semantics of its components and how they interact. Here, we discuss the Synchronous Data Flow (SDF) paradigm, and other graphs that can be derived by applying transformation to an original SDF graph. We focus on the SDF for its relevance for signal processing applications and for reasons we will discuss in this paragraph.

#### **Synchronous Data Flow**

SDF [37] model is very commonly used in DSE work for signal processing applications. SDF is a dataflow paradigm proposed to describe signal processing applications, in a way that concurrency inherent to an application is exposed. The definition of a SDF graph is given in Definition 2.1.1.

**Definition 2.1.1** (SDF graph). A SDF graph *G* is a tuple  $\langle A, E \rangle$  where *A* is a finite set of vertexes denoting computations (called *actors*) and *E* is a finite set of directed edges denoting First In First Out (FIFO) channels between these actors. Any actor can fire (perform its computation) as soon as enough input data (called token) are

available on its incoming arcs. Edges are annotated with a the number of tokens consumed and produced by each actor firing.

In a SDF graph, production and consumption rates of actors are known a priori. SDF allow for static scheduling at design time, thereby, minimizing run time overhead. In SDF, all computations and data communications can be scheduled statically. During DSE, SDF graphs can be analyzed, as such, or after being transformed to other forms.

**Acyclic and Homogeneous Synchronous Data Flow** In order to expose the parallelism in an application (i.e., parallelism of computation, and parallelism of data), a special case of SDF, called Homogeneous Synchronous Data-Flow (HSDF), can be obtained by applying a transformation on the original SDF. In a HSDF graph, the amount of tokens exchanged on edges are homogeneous, i.e., production = consumption. HSDF graphs exhibit the potential parallelism in an application. As such, more options for the mapping of actor firing (task) and data exchange (communication) can be explored, compared to an original SDF graph.

Acyclic Homogeneous Synchronous Data-Flow (AHSDF) is a sub-class of SDF where cycles are banned, i.e., there is no path that starts at a given node, traverses a directed sequence of edges and loops back to the same node. By banning cycles, acyclic graphs are useful to isolate a single iteration of the application. Therefore, the AHSDF both exposes the potential parallelism in an application, and allows to isolate a single iteration of the application.

#### 2.1.2 Processing models: heterogeneity

A processing model refers to the processing resources deployed on the architecture. Heterogeneity of a processing model is described with respect to how different deployed processing resources are from each other. We identify three processing models with respect to their level of heterogeneity.

Homogeneous: Processing resources are all identical (e.g., Kalray MPPA-256 platform [69]).

- Weakly heterogeneous: Processing resources are all identical, but the clock frequency, memory size or other parameters are different.

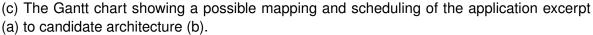

- Strongly heterogeneous: Processing resources can be of different types (e.g., generic CPU, DSPs, computation-specific hardware accelerators): A processing resource may not be able to support the execution of all applications tasks. A processing resource can contain a single Processing Element (PE) (core) for execution or several cores (e.g., multi-core CPU). Examples of real-word architectures with this processing model are the Samsung Exynos and Qualcomm Snapdragon ranges used in smartphone and tablet architectures.

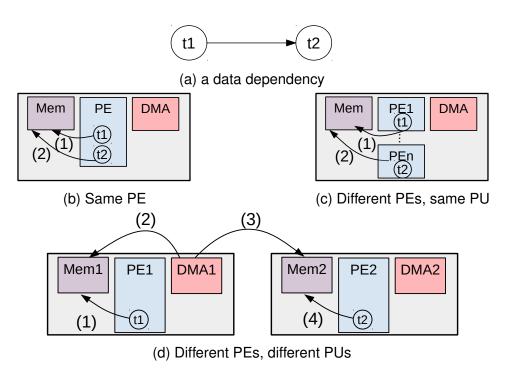

#### 2.1.3 Communication models

Communications of an application need to be mapped and scheduled on the target communication architecture. A communication model describes how communications between different architecture components are captured during DSE. In existing DSE works, several communication models are considered, ranging from assuming instantaneous communications (i.e., communication overhead is assumed negligible), to deeply analyzing a communication structure in order to estimate communication times, e.g., assignment of bus time slots to communications. In the following bullet points, we first overview communication models, where a communication architecture is analyzed in order to derive a mapping and scheduling of communications.

- Single shared bus: This model refers to a single shared bus connecting all components. Here a unique mapping option is available: the shared bus. Since only one component of the bus can have control at a given time, and accounting for the potential parallelism in applications, contention on the shared bus interconnect should be handled during scheduling. Basically, an arbitration policy (e.g., Time Division Multiple Access (TDMA) in [50]) is modeled to estimate communication times on the shared bus.

- Full/Partial crossbar: This model corresponds to the crossbar (or bus matrix) interconnect which operates as multiple buses connecting all components (full crossbar), or a subset of components (partial crossbar). Mapping and scheduling communications on a crossbar require to address some constraints such

as exploiting the parallelism of buses while respecting the capacity of communications between pairs of components.

- Multi-bus Segmented bus: This communication model refers to the multibus interconnect where multiple bus segments are connected to each other, in a certain scheme (e.g., hierarchical, ring, ad-hoc), and components are connected locally to each segment. It allows parallel transfers on different segments leading to less contentions than the single shared bus. However, mapping and scheduling are more complex because each segment can operate at a different bandwidth, tasks and components can be distributed to bus segments in many different ways, many routes can be available, and inter-segment communications have to be handled along with local communications.

- NoC: This model refers to the NoC which is a network structure composed of switches (routers) and links and relying on data packetization: Before being transmitted through the interconnect, data is split into packets. A packet is received by the router in an input buffer, then it is routed to the appropriate output link. Data packets traverse progressively switches and links until reaching the final destination. NoCs are known for being more scalable than bus-based architectures but they are also more complex to design [16]. Therefore, the NoC communication model has been extensively studied [4,52]. DSE for NoCs addresses NoC problems like packetization and depacketization of data.

- **Hybrid:** This category groups works that consider any hybrid combination of buses (shared and segmented), crossbars, and/or NoCs. Mapping and scheduling here account for a meld of design issues from each communication model used.

During DSE, some abstractions can be considered on the analysis of communication mapping and scheduling, resulting in simplified communication models, which do not analyze communications through the interconnect. These models, summarized hereafter, can be applied for any type of communication architecture (e.g., shared bus, NoC).

- **Communication-oblivious:** This model simply assumes that communications between components are instantaneous. Here, the impact of communications on the overall performance is assumed negligible.

- Fully connected Constant latency: This model suggests that all components communicate between each other through dedicated private channels. The communication latency between each pair of components is constant (e.g., defined in a matrix) and is not affected by the co-existing load.

## 2.1.4 Design decisions

An application is built upon a set of tasks and communications between tasks. An architecture is built upon processing, communication and storage resources. In this thesis, we focus on tasks and communications mapping and scheduling on processing and communication resources. We refer to system parameters that are explored and decided during DSE by *design decisions*. A DSE approach can examine one or several design decisions simultaneously. Basically, the complexity of a DSE problem increases with the number of decisions evaluated at once. However, regarding design decisions in an integrated way allows a holistic view of the system parameters and their interdependencies. This holistic view is often necessary to ensure finding optimal design solutions. In the following, we overview design decisions related to the mapping (application-to-architecture) and the scheduling (application-to-time/order).

- **Task Mapping** refers to the assignment of a processing resource from the architecture to each task from the application.

- **Task Scheduling** refers to determining a temporal organization of tasks. Basically, there are two ways to do this: 1) Determining an order of execution of tasks, or 2) Determining the exact start times of each task. From the latter, the former can be deduced.

- **Communication mapping**, or routing refers to the assignment of one or multiple communication resources from the architecture to each data transfer needed between a pair of tasks from the application.

Communication scheduling refers to determining a temporal organization of communications. As for task scheduling, two ways are possible: 1) Determining an order of execution of communications, or 2) Determining the exact times where communications occur on resources. The former can be deduced from the latter as well.

## 2.1.5 Design objectives

A design objective is a goal on a cost or a performance metric (criteria) that a design solution should achieve. A design objective can be of two types: 1) *Satisfy*, meaning the metric should be below or over a given threshold, or 2) *Minimize/Maximize*, meaning the optimal value should be reached for the metric. As an example, a real-time system is typically not required to respond as fast as possible (e.g., *Minimize latency*) but fast enough so that the timing requirement is respected (e.g., *latency*  $\leq$  *threshold*<sub>latency</sub>). However, one can be interested in maximizing the usage of the hardware material deployed (e.g., *Maximize usage*). Higher exploration effort is required to achieve a *Minimize/Maximize* design objective, as shown for example in [26] for latency, and later in our experimental evaluations (Section 4.4, Chapter 4).

In the rest of this subsection, we overview a non-exhaustive list of the most recurring design objectives that we identified in related work. These design objectives can be considered separately or simultaneously in a DSE problem.

#### Latency

Performance design objective on latency has received significant research attention, especially in the real-time community. For a dataflow application graph (e.g., Directed Acyclic Graph (DAG)), latency (or end-to-end latency) refers to the time that separates the end of the last task from the start of the first task. Typically, two types of design objectives are applicable to latency: 1) Satisfy, and 2) Minimize. While the latter aims at providing the design solution which guarantees the lowest latency, the former is content with respecting a certain threshold on latency. For example, while some systems have to respond as fast as possible (e.g., in systems where processing resources can only execute a task at once, without preemption, minimizing la-

tency allows to reduce the time during which processing resources are unavailable), other systems only need to respect a certain time budget or a deadline constraint.

#### Throughput

For periodic applications, throughput is defined as the inverse of the period, i.e., the time it takes to execute an entire iteration of the SDF application graph. Achieving a certain goal for throughput is also a major design objective. As periodic dataflow applications (e.g., streaming applications) run continuously, it is important to assess their data processing rate. Similarly to latency, throughput can be either subject to *Satisfy* constraints (e.g., guaranteeing a minimum throughput), or to *Maximize* objective.

#### **Power consumption**

Power consumption is another important design concern [44]. Low power consumption is a key enabler for portable embedded devices (e.g., smartphones), where various applications should execute while keeping a battery charged longer. Power consumption is also a major concern in server infrastructures where the amount of power consumed tend to be significant [44]. Moreover, power consumption of a System on a Chip (SoC) represents a limit to its integration capacity [31,70].