# Conception d'un circuit intégré pour la visualisation graphique

Philippe Matherat

#### ▶ To cite this version:

Philippe Matherat. Conception d'un circuit intégré pour la visualisation graphique. Micro et nanotechnologies/Microélectronique. Université Pierre et Marie Curie - Paris VI, 1978. Français. NNT: . tel-00177458

## HAL Id: tel-00177458 https://theses.hal.science/tel-00177458

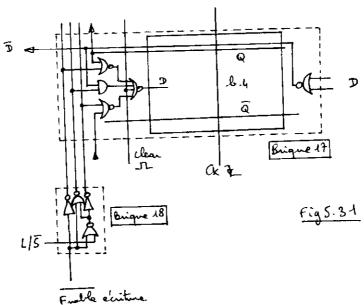

Submitted on 8 Oct 2007

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Philippe MATHERAT

CONCEPTION D'UN CIRCUIT INTEGRE

POUR LA

VISUALISATION GRAPHIQUE

Thèse de Troisième Cycle 19 Mai 1978

#### Résumé :

L'extension de l'utilisation des consoles graphiques est freinée par le prix élevé du matériel existant. Ce coût peut être abaissé par l'utilisation d'un téléviseur. Pour permettre le rafraîchissement d'un tel écran à balayage de trame, il est nécessaire de disposer d'une mémoire d'image où tous les points sont codés sur un bit en Noir et Blanc (ce qui correspond à 256 K bits pour 512 x 512 points), et davantage en couleur. Une telle capacité devient raisonnable vu l'augmentation de densité des mémoires intégrées, à condition que l'électronique de gestion de la mémoire d'image soit simple. L'intégration de celleci en un circuit LSI, comprenant en outre un générateur de vecteurs et de caractères câblé prévu pour un couplage par bus microprocesseur est l'objet de ce travail.

Le circuit permet une grande vitesse d'écriture (1,3 $\mu$  s par point), et une grande versatilité, tant dans le format d'affichage (64 x 64 jusqu'à 512 x 512 points avec un nombre quelconque de niveaux de gris ou de couleurs) que dans le couplage microprocesseur (bus 8 bits bidirectionnel de données, bus d'adresse de 4 bits, signaux de lecture-écriture et requête d'interruption).

Dans le but de simplifier l'implantation topologique d'un tel circuit (équivalent à 2000 portes) très peu répétitif, la structure logique et géométrique d'un ensemble de fonctions de base ("briques") est proposée. La structure fonctionnelle de chacune des parties du circuit est ensuite étudiée, suivie de son implantation topologique, utilisant au mieux les briques précédemment définies.

#### Abstract :

Increased use of graphic display units is prevented by the high cost of existing devices. Lowering their costs suggests the use of TV sets. Display electronics for such a raster-scan unit will include a screen memory containing the state of all displayable points, that is up to 256 K bits for a 512  $\times$  512 B&W display and more for colour applications. Technological advances in NMOS memories make such memory sizes cheaper and cheaper. The control part ensuring screen refresh, memory management, vector and character generation and computer coupling remains very complex. Design of a microprocessor-oriented Large-Scale-Integrated circuit including all these functions is the topic of this work.

The chip permits a decent writing speed of one point per 1,3 $\mu$  s and a great versatibility, as well for screen memory organization as for microprocessor interface. Display resolution from 64 x 64 to 512 x 512 points are possible, with any number of colours or gray levels. Microprocessor interface is standard: an eight bits bidirectionnal data bus, a four bits address bus, readwrite signals and an interrupt request.

In order to simplify the topological layout of such a circuit (equivalent complexity of 2000 gates) of a non-repetitive structure, logical and geometrical design of elementary building blocks is defined. Functional structure of each part of the circuit is then studied, followed by his topological layout using as much as possible the available building blocks.

Je remercie Monsieur le Professeur J. ARSAC d'avoir accepté de présider le jury de cette thèse.

Je remercie Messieurs F. ANCEAU et G. NOGUEZ pour leurs encouragements et leurs suggestions tout au long de ce travail.

Je remercie Monsieur C. GIRAULT pour ses critiques et indications lors de la rédaction.

Je suis très reconnaissant à Monsieur M. JOUMARD ainsi qu'à tous les membres de la SESCOSEM qui ont cru dès le départ à ce projet et grâce auxquels cette étude pourra donner lieu à une réalisation concrète.

Je suis très redevable à J.M. FRAILONG et J. GASTINEL pour les fructueuses discussions qui ont jalonné ce travail. Leurs remarques nombreuses m'ont guidé et c'est avec plaisir que je leur exprime ici mes remerciements.

Je ne saurais oublier de remercier Monsieur M. VALLINO, Directeur du Centre de Calcul de l'Ecole Normale Supérieure pour sa confiance, et les moyens mis à ma disposition, ni les usagers du centre, avec lesquels il m'a été agréable de travailler.

Je remercie enfin Monsieur LETELLIER du service des brevets de la THOMSON pour sa lecture différente du manuscrit et ses corrections.

# CONCEPTION D'UN CIRCUIT INTEGRE POUR LA VISUALISATION GRAPHIQUE

0-Introduction.

1-Choix d'une structure d'unité d'affichage adaptée à l'intégration.

2-Description fonctionnelle du circuit.

3-Méthode d'implantation.

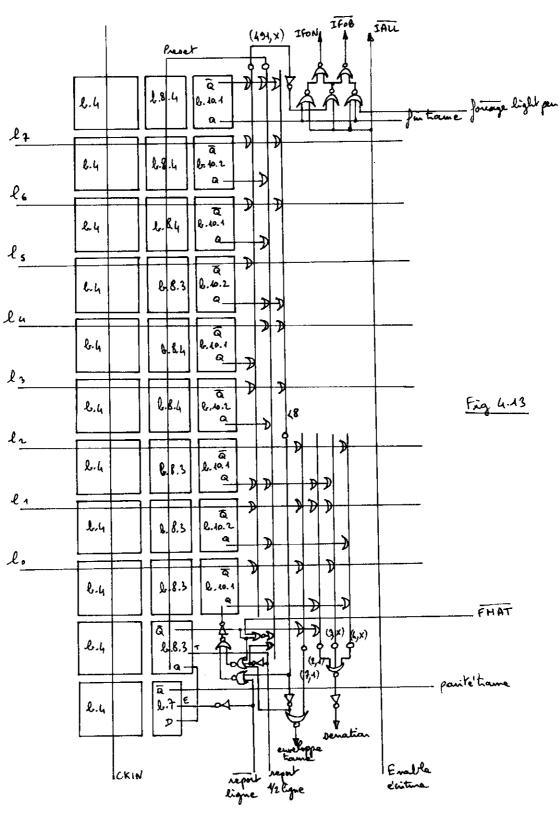

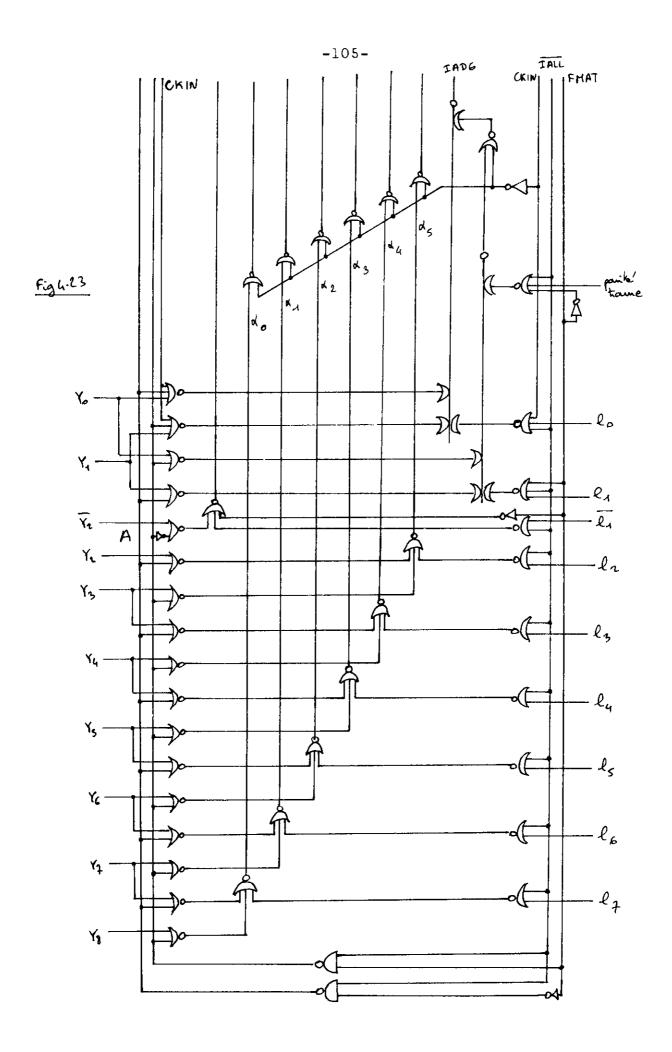

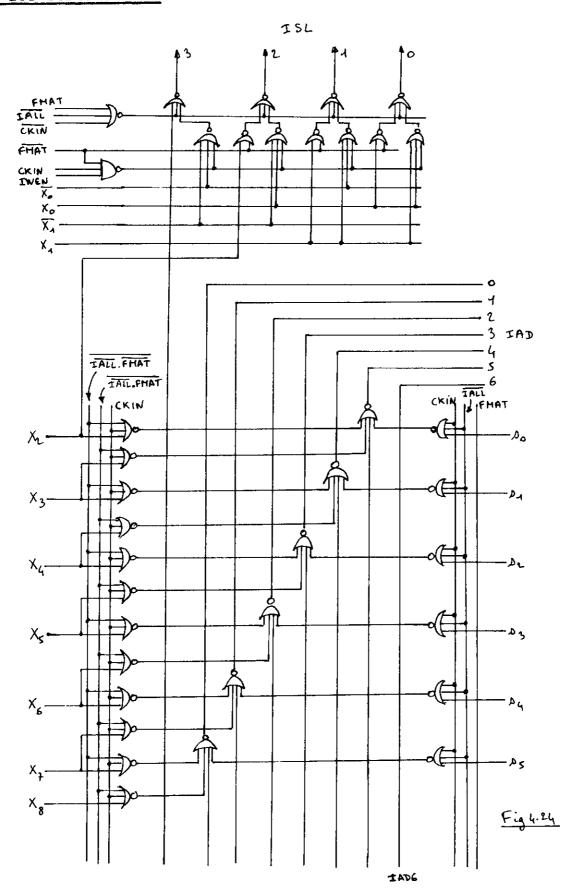

4-Contrôleur de visualisation-synchronisation et gestion de la mémoire d'image.

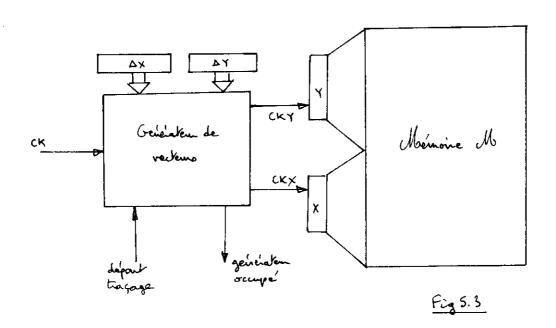

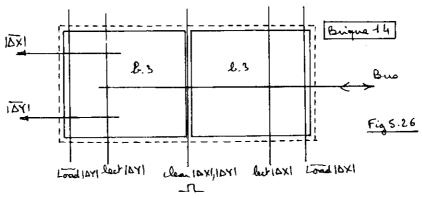

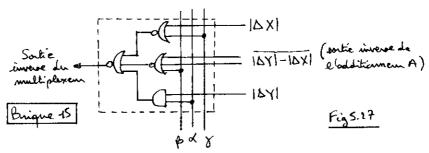

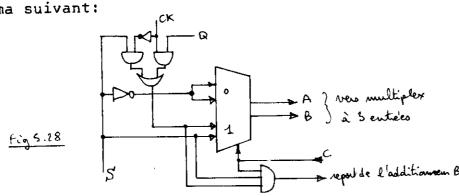

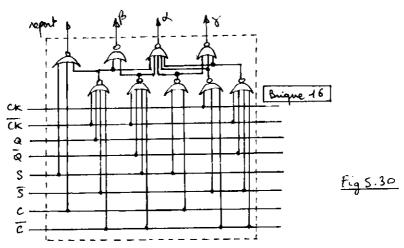

5-Générateur de vecteurs.

6-Générateur de caractères.

7-Logique de contrôle et disposition des sous-ensembles sur la puce.

8-Exemple d'application.

9-Conclusion.

10-Références.

ll-Annexe: brochage du circuit.

### O-INTRODUCTION

Les circuits intégrés réalisés en 1985 atteindront une densité de 5 millions de transistors par boîtier pour des circuits d'organisation comparable aux microprocesseurs actuels. Une densité dix fois supérieure sera atteinte pour des circuits très répétitifs tels que des mémoires. Cette estimation, déduite de la loi de MOORE (1964) -indiquant un doublement tous les ans depuis 1959 et jamais démentiesera certainement vérifiée [1]. En effet, non seulement les lois de la physique n'interdisent pas le fonctionnement de circuits de cette densité, mais les procédés de réalisation sont en cours de mise au point [2]. Ils consistent en le remplacement des rayons lumineux visibles par des électrons ou des rayons-X pour insoler la résine photosensible lors de la photolithographie. La finesse des motifs est alors augmentée dans le rapport des longueurs d'onde des rayonnements utilisés.

Or, une complexité de 5 millions de transistors correspond à un ordinateur IBM 370/168. Il est évidemment exclu que cet ordinateur soit un jour intégré tel quel pour constituer un seul composant, ne serait-ce qu'à cause du nombre trop élevé de connexions avec l'extérieur. La structure des futures machines sera très différente, fortement influencée par des "critères d'intégrabilité". Le parallèlisme sera largement favorisé car il augmente la répétitivité des circuits et facilite leur conception. Les algorithmes classiques ne permettront pas d'utiliser pleinement les possibilités de ces machines, et il faudra étudier des méthodes pour manipuler conceptuellement de telles structures. Ainsi, l'informatique sera probablement révolutionnée jusque dans ses aspects les plus théoriques.

En ce qui concerne la réalisation des ordinateurs, nous commençons à prendre conscience que leur coût n'est pas celui des éléments actifs (portes logiques), mais celui des connexions, tant entre les transistors d'une même "puce", que entre les puces [3]. Ce sont les connexions qui occupent le plus de surface, qui, par leur capacité électrique, diminuent la vitesse de fonctionnement, imposent la taille des transistors, et ainsi dictent la consommation électrique et la dissipation de chaleur. En outre, elles causent la quasitotalité des pannes. Ceci justifie l'étude d'une nouvelle théorie des machines logiques, cherchant à minimiser non pas le nombre d'opérateurs de base nécessaires pour réaliser la fonction, mais la surface occupée par cette fonction. Il est en effet souvent intéressant de calculer plusieurs fois une variable logique en des "endroits" différents afin de supprimer les connexions nécessaires pour la transmettre. Une telle théorie tenant compte de considérations topologiques devrait manipuler comme un tout à la fois la fonction logique et l'implantation géométrique de cette fonction.

Avant d'étudier ces problèmes, nous avons beaucoup à faire pour nous mettre au courant des méthodes actuelles de réalisation des microcircuits, non pas les techniques chimiques et physiques de leur fabrication mais les méthodes de conception logique qui prennent place avant la réalisation des masques. Nous avons choisi à cette occasion de concevoir un composant qui, associé à un récepteur de télévision, permette de réaliser une console de visualisation graphique. Il est intéressant de constater que cette technique d'affichage (à balayage de trame) -qui oblige à mémoriser individuellement chaque point de l'écran pour les envoyer séquentiellement sous forme de signal vidéo- aurait parue tout à fait mal choisie il y a seulement 5 ans. Aujourd'hui, vu l'augmentation de densité des mé-

moires et la possibilité de réaliser toute l'électronique de gestion en un seul circuit intégré, il semble que ce soit le moyen qui permette, grâce à son faible coût, une réelle utilisation massive des consoles graphiques interactives.

En effet, un terminal interactif n'est efficace et ne fait gagner du temps à l'utilisateur que si celui-ci est présent devant l'écran pendant un temps assez long. Pourtant, aujourd'hui, dans les grands centres de calculs, il n'existe que quelques rares exemplaires de consoles graphiques, dont l'utilisation est facturée très cher.

Par ailleurs, ce besoin de consoles graphiques apparaît d'une autre façon: on commence à voir des miniordinateurs bon marché destinés à tous, comme les calculatrices de poche actuelles mais comportant un clavier et un écran de visualisation. Il est aisé de prédire à ces appareils une grande réussite commerciale. Ils pourront effectuer toutes sortes de traitements locaux, et pourront dans un avenir pas très lointain être connectés à de grands centres de "Time-Sharing" offrant leurs services par l'intermédiaire du téléphone (compagnies aériennes ou de chemins de fer pour les réservations, magasins de vente par correspondance, et surtout agences de presse, cours par correspondance, bibliothèques etc...)[4]. Ces miniordinateurs s'adresseront à des non-informaticiens, et devront être dotés de langages de haut niveau, utilisant largement l'affichage graphique [5]. Ceci ne sera possible qu'à la condition de disposer de consoles bon marché, mais possédant tout de même d'excellentes performances: définition suffisante, possibilités d'affichage en couleur et surtout une vitesse de tracé élevée. Cette dernière caractéristique permet l'affichage d'images en mouvement, et l'affichage rapide de figures fixes compliquées, ce qui est essentiel pour une

utilisation interactive efficace.

Le travail exposé ici présente la structure d'une unité de visualisation à balayage de trame, puis montre comment on peut en détacher une partie se prêtant bien à l'intégration, en tenant compte des contraintes de réalisation, mais aussi en recherchant la versatilité de l'objet qui devra ensuite être utilisé en tant que "boîte noire".

Le premier chapitre compare les différentes structures d'unités d'affichage et fixe les choix fondamentaux concernant la fonction du circuit intégré: circuit d'adressage d'une mémoire d'image graphique entièrement lue périodiquement lors de la visualisation, et accédée point par point en écriture par un générateur câblé de vecteurs et de caractères commandé de l'extérieur par un bus microprocesseur.

Les choix de détail dépendant de notre réalisation sont énumérés dans le second chapitre. Ils sont souvent basés sur une prévision des montages et des programmes utilisant le circuit et attendent une justification à postériori.

Avant de passer à une description précise du fonctionnement de chaque partie du circuit, le troisième chapitre expose la méthode d'implantation choisie qui dicte la structure logique des éléments, rejaillissant sur l'exposition des chapitres suivants. Ce chapitre se termine sur la proposition des schémas logiques des "briques" fonctionnelles d'une bibliothèque de base.

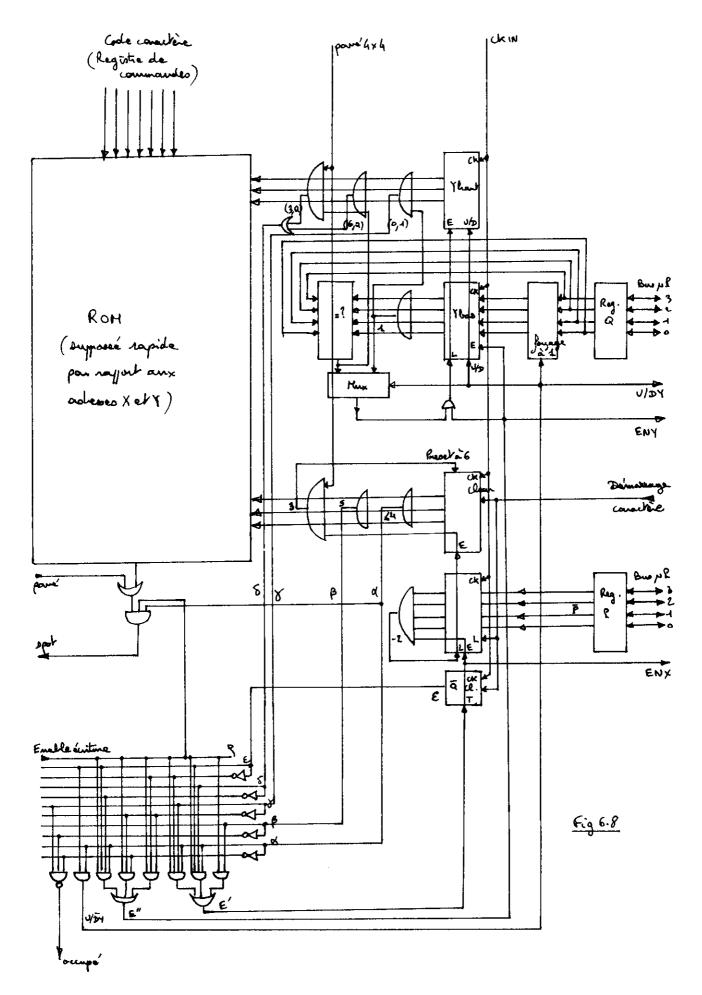

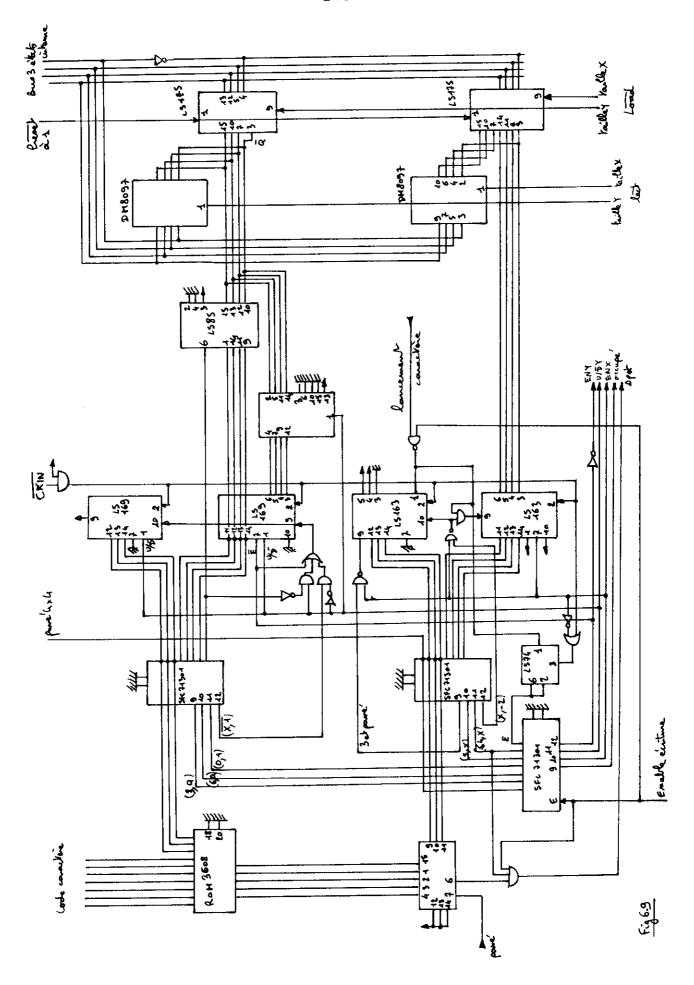

Les chapitres qui suivent (4,5,6, et 7) exposent en détails le fonctionnement des différentes parties du circuit et débouchent chacun sur deux schémas: l'un décrit le montage de simulation réalisé à partir de circuits existants, l'autre est la symbolisation à partir de portes élémentaires, permettant d'entreprendre le dessin des

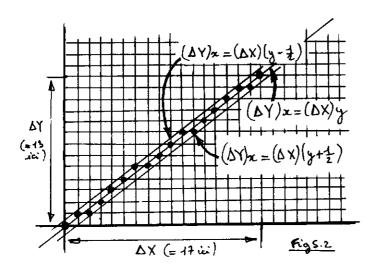

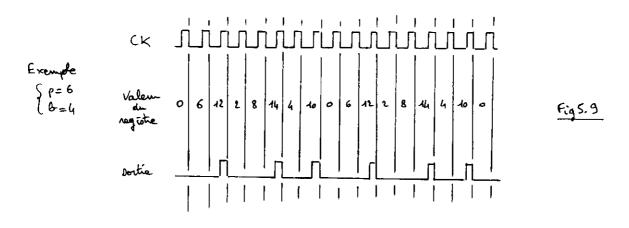

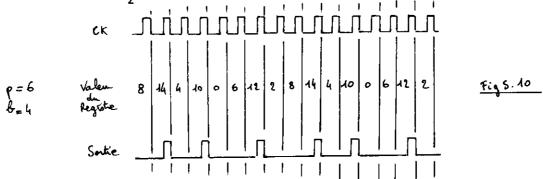

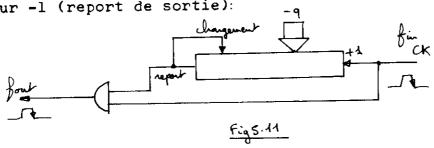

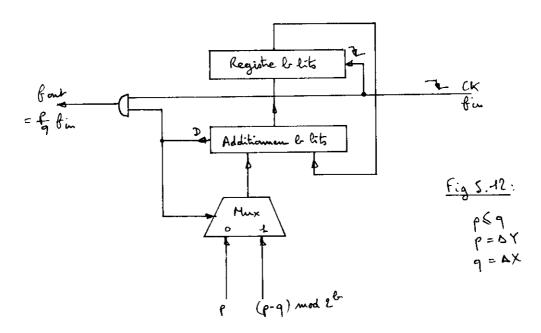

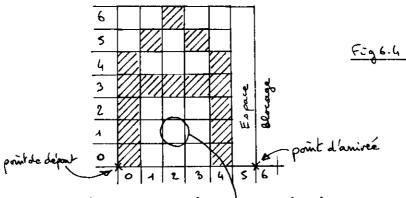

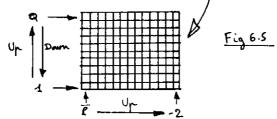

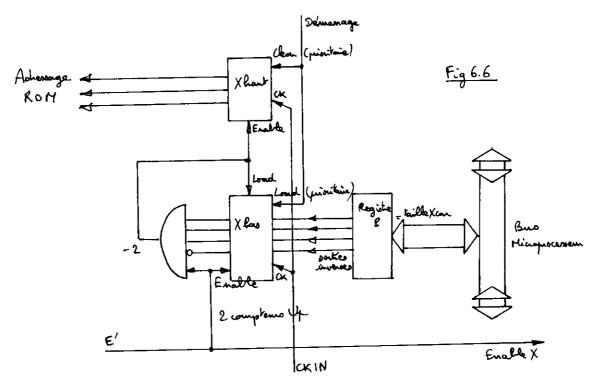

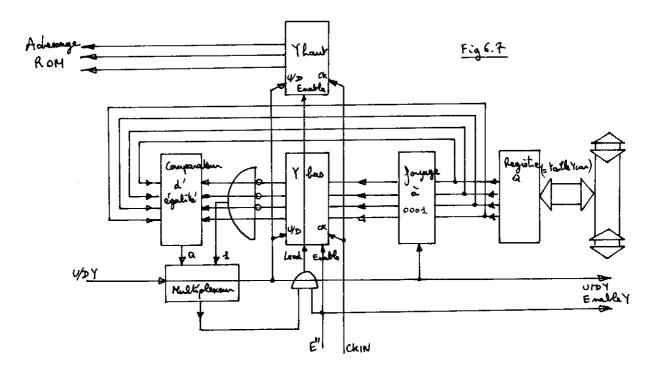

masques du circuit intégré. Le chapitre 5 en particulier décrit la structure du générateur de vecteurs câblé qui adresse à chaque période d'horloge un nouveau point du vecteur à tracer. Nous montrons que l'approximation du vecteur obtenue est la même que celle de l'algorithme classique de génération programmée de vecteurs.

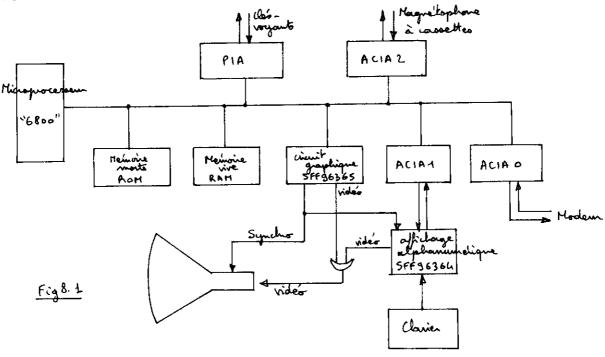

Une application de ce circuit à la simulation d'une console graphique très répandue est exposée dans le huitième chapitre.

## 1-CHOIX D'UNE STRUCTURE D'UNITE D'AFFICHAGE ADAPTEE A L'INTEGRATION

- 1.1-Constituants indispensables d'une unité d'affichage.

- 1.2-Les différents types d'écran.

- 1.3-Les différentes structures d'unité d'affichage.

- a)Tube à mémoire et balayage cavalier.

- b) Tube sans mémoire et balayage cavalier.

- c) Tube sans mémoire et balayage de trame.

- 1.4-Avantages et inconvénients de chaque structure.

- a)Résolution.

- b)Possibilité d'affichage en couleurs.

- c)Limitation du nombre de traits affichés.

- d)Effacement sélectif.

- e)Figures en mouvement.

- f)Coût des composants.

- 1.5-Choix du balayage de trame.

- 1.6-Codage de la figure au niveau du terminal.

- 1.7-Quel type de mémoire utiliser pour le codage des points?

- 1.8-Choix des performances du système d'écriture.

- 1.9-Choix du dispositif de couplage avec l'extérieur.

- 1.10-Conclusion.

# 1.1-CONSTITUANTS INDISPENSABLES D'UNE UNITE D'AFFICHAGE

L'information graphique est rarement manipulée sous la forme d'une liste des états de tous les points composant une image. Tant dans le but de diminuer la quantité d'information à stocker ou à échanger que pour simplifier les algorithmes de traitement, on utilise un codage sous forme de listes de "vecteurs" et de "caractères". Un vecteur est défini par les coordonnées de son origine et de son extrémité ou par les longueurs de ses projections sur les axes de coordonnées. Un caractère est défini par son numéro d'ordre dans une liste (jeu de caractères). La manipulation d'une image se fait alors en termes d'ajouts ou de retraits de vecteurs ou de caractères.

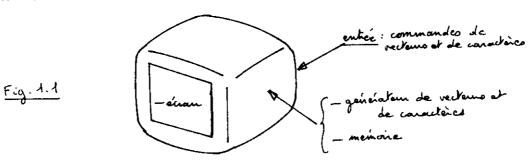

Une unité d'affichage comporte donc toujours 3 éléments fondamentaux:

- -l'écran, dont le rôle est d'émettre de la lumière,

- -le <u>générateur</u> <u>de vecteurs et de caractères</u>, qui transforme la description codée en une description point à point,

- -une <u>mémoire</u>, permettant de tenir à jour l'état de l'image affichée.

## 1.2-LES DIFFERENTS TYPES D'ECRAN

La structure des 2 derniers éléments dépend fortement du premier. Aujourd'hui, toutes les unités d'affichage graphique disponibles sur le marché utilisent un tube à rayons cathodiques (CRT) [6]. De nombreux autres dispositifs sont à l'étude, basés sur les propriétés des cristaux liquides, des diodes électroluminescentes ou des plasmas, mais aucun n'a encore débouché sur une réalisation commerciale.

Ces CRTs, indépendemment de la possibilité éventuelle d'afficher des images en couleurs, peuvent se distinguer suivant 2 critères:

-certains sont "à mémoire". Dans ce cas, un point de l'écran atteint une seule fois par le faisceau d'électrons reste lumineux. L'image ne peut alors être effacée que sur toute sa surface en même temps, et cette opération est relativement longue (plusieurs dizièmes de secondes). Par contre, dans le cas d'un écran sans mémoire, un point n'est lumineux que pendant un court temps après le passage du faisceau d'électrons. Ce temps de "rémanence" est en général inférieur à 100µs -sauf dans le cas des radars- et inférieur au temps de parcours d'une ligne dans le cas de la télévision N&B. Le faisceau d'électrons doit alors constamment répéter son parcours pour "rafraîchir" l'écran, avec une période inférieure à la persistance rétinienne.

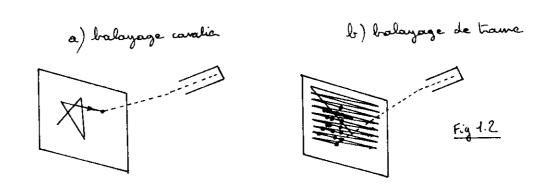

-le balayage du faisceau peut être "cavalier" ou "de trame".

Dans le premier cas, le faisceau ne parcourt que les points à allumer et à intensité constante (sauf pour sauter d'une partie de la figure à une autre non connexe). Dans le cas du balayage de trame, la totalité de la surface de l'écran est constamment balayée par le faisceau qui suit toujours le même chemin quelquesoit la figure affichée. Il faut alors moduler l'intensité du faisceau en fonction

de l'appartenance du point atteint à la figure affichée. Le parcours s'effectue généralement de gauche à droite à une fréquence voisine de 20kHz et de haut en bas à une fréquence voisine de 50Hz.

# 1.3-LES DIFFERENTES STRUCTURES D'UNITE D'AFFICHAGE

En fonction de ces 2 critères de distinction des CRTs, on peut classer les unités d'affichage en 3 groupes dans lesquels les constituants fondamentaux sont organisés différemment:

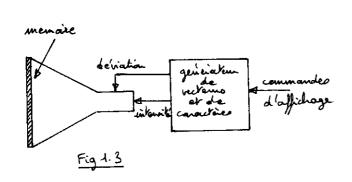

a) <u>Tube à mémoire et balayage cavalier</u>. C'est la structure des consoles TEXTRONIX de la série 4010 [22].

- -L'écran mémorise l'image point à point.

- -Le générateur de vecteurs et d'affichage de caractères commande la déviation du faisceau.

- b) Tube sans mémoire et balayage cavalier. C'est en particulier la structure des unités IBM 2250, et du mode "non marquant" des TEXTRONIX du haut de la gamme 4010 (dans ce mode, et sur ces modèles, l'énergie fournie par le faisceau d'électrons est choisie faible pour éviter d'inscrire l'image dans la mémoire du tube).

-L'image est codée en mémoire sous forme d'une liste de vecteurs et de caractères.

-Le générateur de vecteurs et de caractères commande la déviation du faisceau.

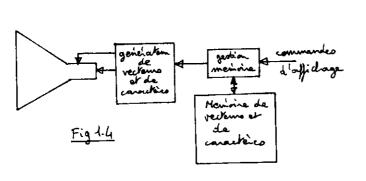

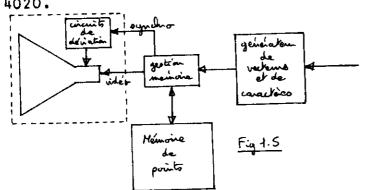

c) <u>Tube sans mémoire et balayage de trame</u>. C'est le cas des nouvelles unités HEWLETT-PACKARD 2648A [10] et TEKTRONIX de la série 4020.

- -L'état de chacun des points est mémorisé.

- -Le générateur de vecteurs et de caractères est constitué de circuits digitaux modifiant la mémoire de points.

Il faut adjoindre dans ce cas des circuits de déviation (synchronisés avec la lecture de la mémoire de points) puisque le trajet du spot est indépendant de la figure affichée. Un récepteur de télévision réalise la fonction encadrée en pointillés sur la figure 1.5.

Un écran à mémoire associé à un balayage de trame présente peu d'intérêt, puisque l'affichage d'une seule trame nécessite déjà la mémoire de points.

## 1.4-AVANTAGES ET INCONVENIENTS DE CHAQUE STRUCTURE

- a)Résolution. La précision des tubes à balayage cavalier est toujours supérieure à 1000x1000 points. Celle des tubes à balayage de trame est limitée verticalement par le nombre de lignes, horizontalement par la bande passante des circuits électroniques, et peut difficilement atteindre cette valeur. Elle est aussi limitée par la dimension et le coût de la mémoire de points, mais cette limite disparaît aujourd'hui puisqu'elle rejoint la définition de 1000x1000points.

- b) Possibilité d'affichage en couleur. Les tubes à mémoire en couleurs n'existent pas.

- c)Limitation du nombre de traits affichés. Le cas des tubes à balayage cavalier sans mémoire est particulier: la fréquence de rafraîchissement est liée à la longueur totale des traits affichés (ou au nombre de traits suivant le cas). Au delà d'une certaine complexité, l'image scintille.

- d) Effacement sélectif. Les écrans à mémoire ne permettent pas d'effacer séparément un trait de la figure.

- e) <u>Figures en mouvement.</u> Les écrans à mémoire ne le permettent pas. Les écrans à balayage de trame sont limités par la vitesse de mise à jour de la mémoire de points.

- f) Coût des composants. Le coût comprend celui du tube, plus élevé dans le cas des tubes à mémoire, et le coût de l'électronique de commande, plus élevé dans le cas du balayage de trame.

## 1.5-CHOIX DU BALAYAGE DE TRAME

L'argument concernant le coût est celui qui fait le plus évoluer la structure des unités d'affichage. En effet, les tubes à balayage de trame ont pour seul défaut intrinsèque une résolution légèrement plus faible. Or, ils ont été longtemps rejetés du fait de la complexité plus grande de l'électronique de commande. Aujourd'hui, la situation change dans la mesure où ces circuits sont intégrables, et où le coût d'un montage électronique dépend davantage du nombre de ses composants que de la nature de ceux-ci. En outre, la structure des unités à balayage de trame a l'énorme avantage de coîncider en partie avec la fonction réalisée par les téléviseurs, ce qui permet un coût encore plus faible vu le marché de ces appareils, sans compter qu'une grande partie des applications concerne l'informatique à domicile, où les téléviseurs existent déjà. D'autre part, l'importance de ce marché garantit que tous les futurs procédés physiques d'affichage seront adaptés aux téléviseurs et donc aux consoles qui les utilisent.

#### 1.6-CODAGE DE LA FIGURE AU NIVEAU DU TERMINAL

Nous avons dit que dans le cas du balayage de trame, la mémoire est une mémoire de points. Ceci est dicté par le problème suivant: le signal vidéo représente à tout moment la fonction logique: { le point atteint par le faisceau d'électrons appartiend à la figure affichée }. Pour une définition horizontale de 500 points, cette fonction doit être évaluée tous les 100ns. Le codage de la figure au niveau du terminal doit permettre d'atteindre cette vitesse.

Si la figure est codée sous forme d'une liste de vecteurs, l'évaluation de cette fonction au point de coordonnées (x,y) se fait par l'exécution de la séquence suivante: (impossible en 100ns)

début vidéo:=faux; pour i depuis l jusqu'à n tantque rvidéo

faire vidéo:= $(x \in [x_{,i}, x_{,i} + \Delta x_{,i}])$  et  $(y \in [y_{,i}, y_{,i} + \Delta y_{,i}])$  et  $(x - x_{,i} - y - y_{,i})$ fait fin

(où la liste comprend n vecteurs, définis par leurs coordonnées d'origine  $(x_{ai}, y_{i})$  et leurs projections sur les axes  $(\Delta x_{i}, \Delta y_{i})$ .

Pour certains types de figures, il est possible de trouver un codage plus dense. En effet, si toutes les figures représentées sont constituées de la répétition sans rotations ni homothéties d'un petit nombre de petites sous-figures, alors il est possible de coder l'image sous forme de 2 listes: une liste donnant la définition point par point des sous-figures, une autre liste donnant les coordonnées des occurences de ces sous-figures [7]. Un câblage spécifique, adapté aux dimensions de chacune des listes, peut générer le signal vidéo assez rapidement.

Mais cette méthode n'est pas utilisable pour une unité d' affichage à usage général, car elle restreind l'ensemble des figures affichables à une classe particulière.

## 1.7-QUEL TYPE DE MEMOIRE UTILISER POUR LE CODAGE DES POINTS?

Les mémoires les plus denses disponibles actuellement sont des 64 Kbits CCD (charge coupled devices). Ces circuits sont organisés en registres à décalage et sont particulièrement adaptés à une sérialisation des données. Ceci est un avantage pour la génération du signal vidéo. Mais l'écriture de nouveaux éléments dans cette mémoire devient alors très problématique. Deux solutions se présentent: On peut attendre qu'une adresse soit utilisée en lecture pour modifier le contenu. Ceci limite alors la vitesse d'écriture des vecteurs à 1 par trame (50/s). Une autre solution consiste à utiliser un "buffer" intermédiaire dans lequel écrit le générateur de vecteurs et de caractères, et qui est transféré à la mémoire lors de la visualisation.

Devant les inconvénients de ces solutions, nous avons préféré

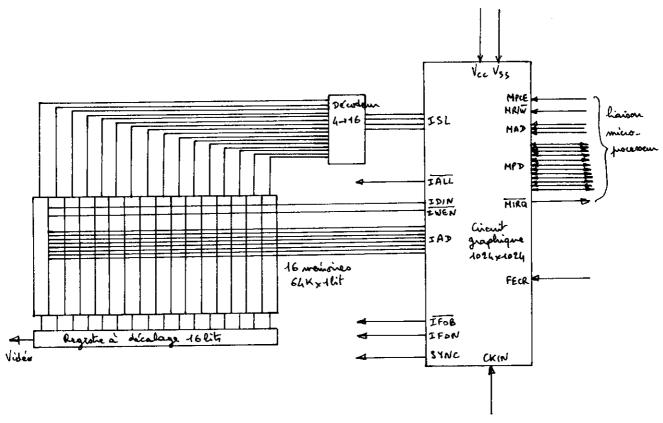

coder les points de l'image dans des mémoires à accès aléatoire (RAM). La densité actuelle est 16 Kbits/boîtier, ce qui correspond à 16 boîtiers pour un affichage 512x512 N&B. La lecture séquentielle périodique de visualisation permet de ne pas se poser le problème du rafraîchissement de ces mémoires dynamiques.

# 1.8-CHOIX DES PERFORMANCES DU SYSTEME D'ECRITURE

Toutes les réalisations actuelles utilisant une telle mémoire d'image et destinées à des affichages de faible coût n'offrent comme possibilités d'écriture que de modifier le point adressé par 2 registres X et Y, seuls registres accessibles par une unité de traitement (c'est le cas notamment des VRAMs de MATROX [9] et des circuits alphanumériques utilisés pour l'affichage graphique). Il faut alors tracer tous les vecteurs et les caractères à l'aide de générateurs programmés. Outre la place mémoire occupée par ces programmes, le temps d'écriture est trop grand (au moins 50µs/point) incomparable avec celui des unités d'affichage de qualité ( $\simeq$ 50µs par vecteur). Il est indispensable pour une utilisation informatique de disposer d'un générateur de vecteurs et de caractères câblé.

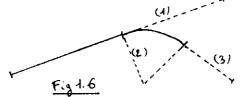

Nous n'avons pas implémenté de générateur d'arcs de cercles. Cela nécessiterait une transformation des paramètres avec laquelle la structure choisie est peu compatible. Il serait intéressant d'envisager cette extension en prévision de l'augmentation des densités d'intégration. A notre avis, le paramétrage intéressant serait: la tangente initiale (1) (donnée par les paramètres du

vecteur précédent), le rayon de courbure (2), et la tangente finale (3).

# 1.9-CHOIX DU DISPOSITIF DE COUPLAGE AVEC L'EXTERIEUR

Nous avons choisi un mode de couplage par bus microprocesseur. Aujourd'hui, un microprocesseur est d'utilisation aussi simple que tout autre composant. Son ajout indispensable à l'unité d'affichage n'enlève pas de possibilités à celle-ci, mais permet l'interfaçage simple avec toutes sortes de coupleurs. Ce microprocesseur pourra être un dispositif de transcodage pour émuler le code des autres unités existantes et permettra ainsi d'utiliser leurs logiciels (voir chapitre 8). Il pourra être le principal organe de traitement dans le cas de petits systèmes, ou un organe permettant de décharger un gros ordinateur sur lequel l'unité est connectée. En particulier, si cette connexion est une ligne à basse vitesse (réseau téléphonique commuté par exemple), le microprocesseur peut être un instrument de compression-décompression de l'information, qui associé à un programme semblable sur le gros ordinateur, permet d'utiliser au mieux les possibilités de la ligne.

## 1.10-CONCLUSION

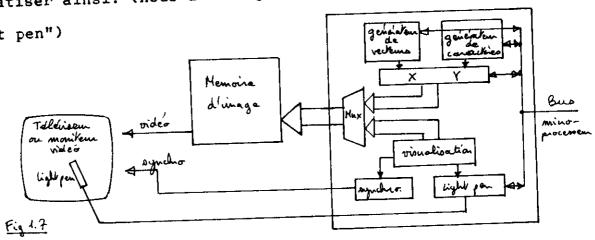

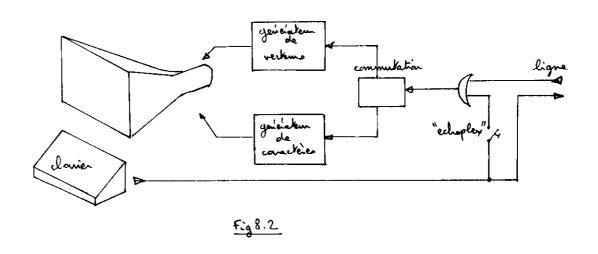

Tous ces choix nous conduisent à une structure qui peut se schématiser ainsi: (nous avons ajouté un circuit de gestion d'un "light pen")

Nous proposons d'intégrer la partie encadrée. C'est un ensemble qui est nécessaire tel quel à toutes les unités d'affichage à balayage de trame, alors que la mémoire d'image par contre dépend des particularités de chaque réalisation: résolution, couleurs, niveaux de gris, superposition d'images, etc...

Cette structure de circuit, tout en offrant un maximum de possibilités, en particulier une grande vitesse d'inscription, ne pénalise pas les utilisations simples où le générateur de vecteurs et de caractères est inutile. Il mérite donc d'être considéré comme un composant à part entière, se définissant indépendemment d'une utilisation particulière.

#### 2-DESCRIPTION FONCTIONNELLE DU CIRCUIT

- 2.1-Rappel: codage de l'information pour un téléviseur.

- 2.2-Rappel: utilisation des mémoires dynamiques 16 broches 4Kxlbits et 16Kxlbits.

- 2.3-Organisation de la mémoire d'image.

- 2.4-Sélection des boîtiers mémoires.

- 2.5-Signaux de contrôle mémoire.

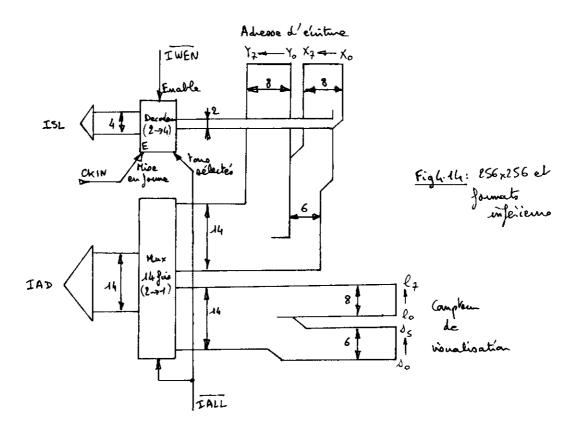

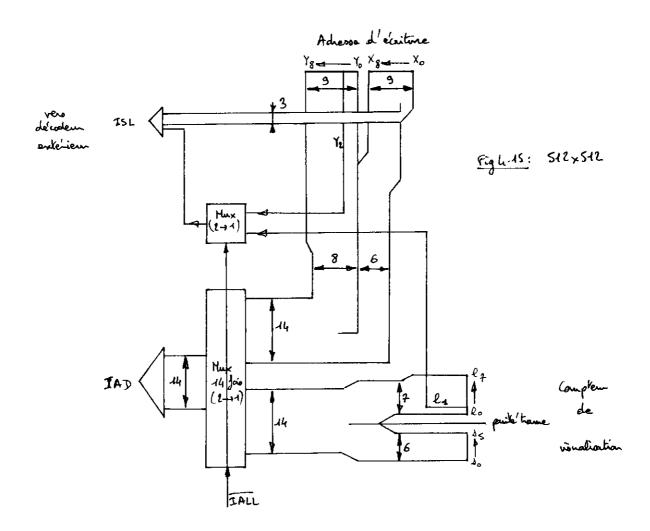

- 2.6-Exemples de montages (Noir et Blanc).

- a)64x64 points.

- b)128x128 points.

- c)256x256 points.

- d)512x512 points.

- e)Autres formats.

- 2.7-Signal de synchronisation.

- 2.8-Récapitulation pour la partie visualisation.

- 2.9-Système d'écriture.

- 2.10-Registres X et Y.

- 2,11-Générateur de vecteurs.

- 2.12-Générateur de caractères.

- 2.13-Light pen et Réticule.

- 2.14-Mécanisme d'effacement de l'image entière.

- 2.15-Mécanisme d'interruption.

- 2.16-Lecture d'un point de la mémoire d'image.

- 2.17-Liaison au bus microprocesseur.

- 2.18-Récapitulation des codes.

Le but de ce chapitre est d'énumérer les particularités du circuit réalisé avant de passer à l'étude de son fonctionnement et de sa conception logique proprement dite. Certaines caractéristiques du circuit sont imposées: les fréquences de balayage ligne et trame et la forme des signaux de synchronisation sont imposés par l'utilisation d'un téléviseur standard; l'adressage de la mémoire d'image est imposé par l'utilisation des mémoires les plus intégrées disponibles actuellement. Les autres caractéristiques ont fait l'objet de choix guidés par des essais de montages et de programmes d'application.

# 2.1-RAPPEL: CODAGE DE L'INFORMATION POUR UN TELEVISEUR [11]

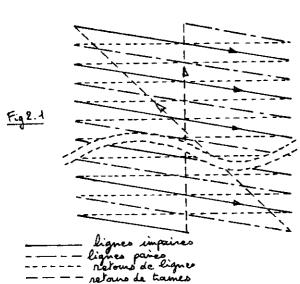

Le faisceau d'électrons balaye constamment la totalité de la surface de l'écran suivant le trajet indiqué en figure 2.1.

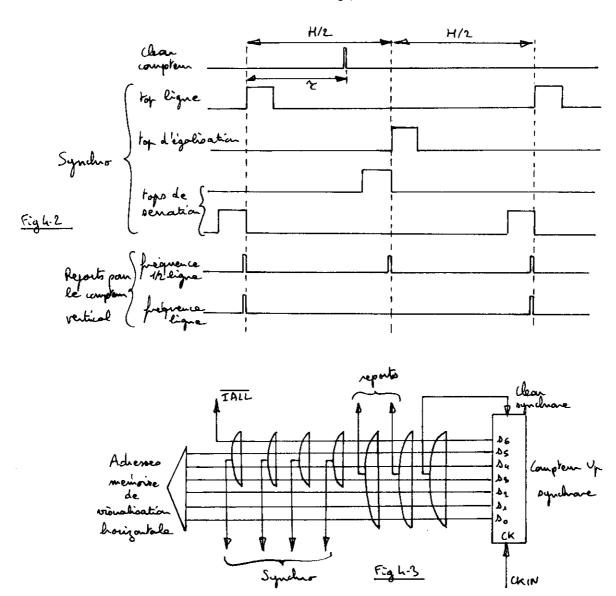

L'écran est parcouru en entier 25 fois par sec. Chacun de ces parcours ("image") comporte 625 lignes, tracées en 2 passes ("trames") de 312,5 lignes, une trame pour les lignes paires, une pour les lignes impaires. On dit qu'il y a "entrelacement" des trames.

A chaque instant, un signal de "luminance" indique l'intensité du faisceau d'électrons correspondant à sa position. La déviation du faisceau est assurée par 2 bases de temps incluses dans le récepteur de télévision auxquelles il faut fournir des signaux de

synchronisation pour ajuster précisément leurs périodes et leurs phases.

2 signaux sont donc nécessaires pour commander un récepteur TV N&B: -la luminance (signal "vidéo"),

-la synchronisation (signal "synchro").

(Ces 2 signaux sont additionnés pour constituer le signal "vidéo composite" dans le cas de l'émission sur une onde porteuse UHF).

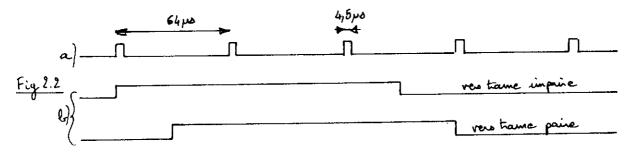

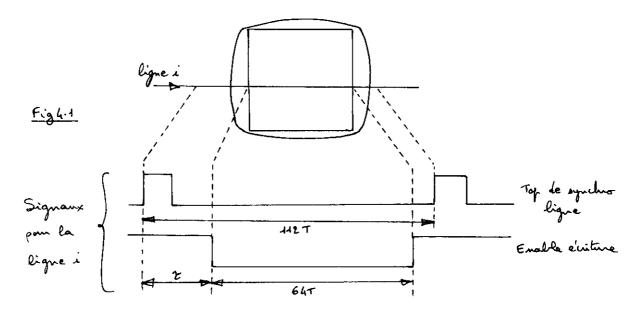

Les "tops" nécessaires à la synchronisation sont les suivants: -un retour ligne est commandé par un top ligne de durée 4,5 $\mu$ s toutes les 64 $\mu$ s (= $\frac{1}{25x625}$ s) Fig 2.2.a,

-un retour trame est commandé par un top trame d'une durée de 2,5 lignes toutes les 20ms Fig 2.2.b.

Pour assurer l'entrelacement, un top trame sur deux doit commencer en même temps qu'un top ligne, un sur deux doit commencer en milieu de ligne.

Pour transmettre un signal unique de synchro, on utilise le OU logique de ces 2 signaux. Le téléviseur les "trie" de la façon suivante:

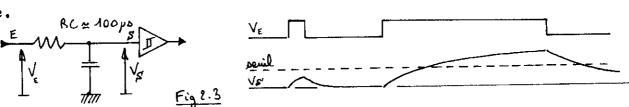

-un intégrateur suivi d'un circuit à seuil permet de reconnaître le top trame (Fig 2.3). La sortie S commande directement le retour trame.

-un différentiateur permet de reconnaître le top ligne (Fig 2.4). La sortie S ne commande pas directement le retour ligne, mais asservie l'oscillateur ligne par l'intermédiaire d'un comparateur de phase.

Le signal de la Fig.2.2 n'est pas satisfaisant car:

- -l'information de synchro ligne disparaît lors du top trame,

- -l'intégrateur n'est pas dans le même état avant un top trame si celui-ci arrive 64µs ou 32µs après un top ligne.

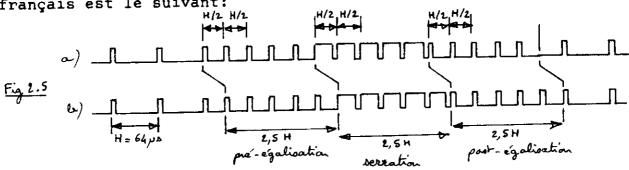

Pour ces raisons, le signal de synchronisation du standard français est le suivant:

Ceci permet de garder l'asservissement de l'oscillateur ligne lors d'un top trame, et de présenter à l'intégrateur un top trame toujours environné de la même façon.

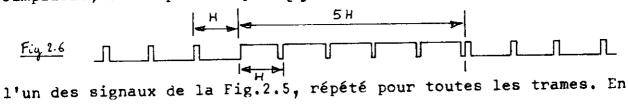

Si l'on veut décrire une image dont la définition verticale est inférieure à  $\frac{625}{2}$  lignes, il est recommandé de réaliser 50 trames identiques par secondes, c'est à dire de cadrer tous les tops trames de la même façon par rapport aux tops ligne. L'image, non entrelacée, paraît plus stable sur l'écran. Le signal de synchro peut être simplifié, comme par exemple ([8]) en Fig.2.6, mais il peût aussi être

particulier, nous avons utilisé celui de la Fig.2.5.b.

En couleur, le signal de synchronisation est identique. Le signal vidéo porte une information de luminance et une de chrominance. Le codage utilisé en télévision ne permet pas une définition supérieure à 160x160 points pour l'information de couleur. On doit alors commander directement les 3 canons à électrons Rouge, Vert et Bleu (entrée R,V,B+Synchro) si l'on désire une définition de 500x500 points pour la couleur.

# 2.2-RAPPEL: UTILISATION DES MEMOIRES DYNAMIQUES 16 BROCHES 4Kx1BITS ET 16Kx1BITS [12], [13]

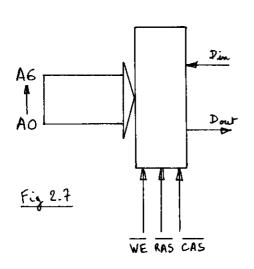

Ce sont des mémoires dynamiques à adressage multiplexé.

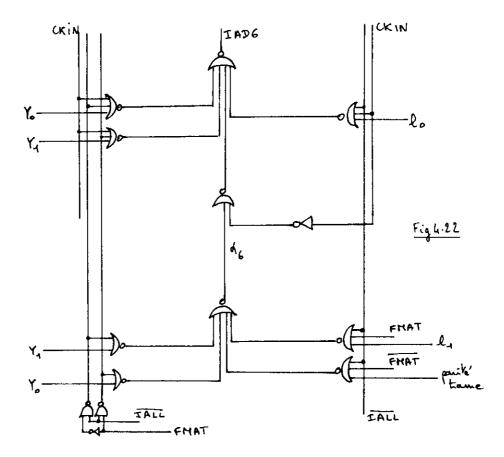

La mémoire 16K est internement organisée suivant une matrice de 128 rangées et 128 colonnes.

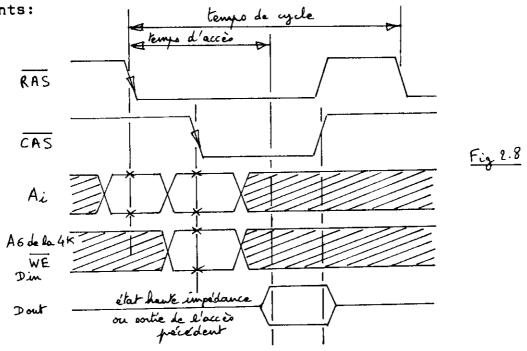

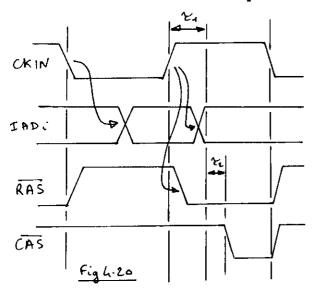

Le front avant de RAS (Row address select) échantillonne la première partie de l'adresse (ou partie basse) -voir Fig.2.8.

Le front avant de CAS (Column address select) échantillonne la deuxième partie (haute) de l'adresse.

Dans le cas de la 4K, A6 sert de sélection de boîtier (CS, actif bas):-il est ignoré sur RAS,

-il est échantillonné sur CAS.

Il faut toujours avoir à l'esprit que la mémoire contient autant d'amplificateurs de rafraîchissement que de colonnes, si bien que lors d'un accès, toute une rangée est rafraîchie. Dans le cas d'un accès séquentiel à tous les bits, le bon rafraîchissement s'opère

donc en faisant varier plus rapidement les adresses de rangées que celles de colonnes.

Par la suite (chapitre 4), nous nommerons les bits d'adresse: RO,R1,R2,...,R6,CO,Cl,...,C6.

Pour généraliser (en oubliant les petites variantes entre les mémoires des différentes firmes), les chronogrammes d'accès sont les suivants:

-WE (Write Enable) indique s'il s'agit d'un cycle de lecture ou d'écriture.

-La donnée d'entrée (Din) est échantillonnée sur CAS.

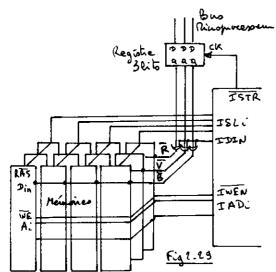

-Dans tous les cas, si RAS ou CAS manque, le boîtier n'est pas concerné par l'accès mémoire. Nous utiliserons cette propriété pour sélecter les boîtiers par l'intermédiaire du RAS, le CAS étant constamment généré pour tous les boîtiers.

## 2.3-ORGANISATION DE LA MEMOIRE D'IMAGE

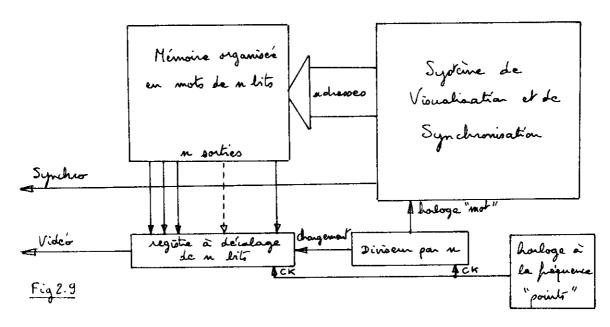

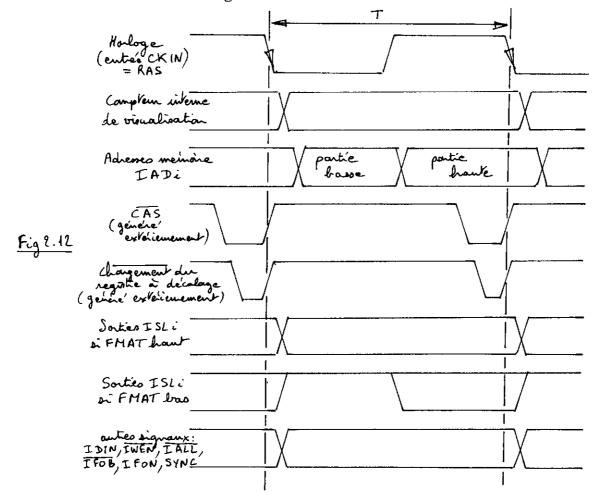

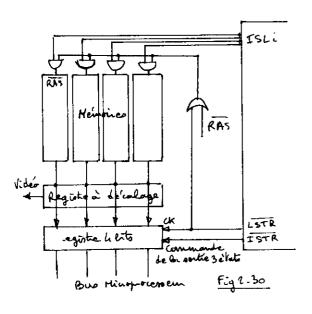

Le signal vidéo décrit successivement l'état de chacun des points d'une même ligne, et nous avons vu qu'à une définition horizontale de 500 points correspond une période de 100ns par point environ. Le temps de cycle des mémoires actuelles étant de 350ns, il est impératif de lire plusieurs points en même temps, différants uniquement par la partie faible de leur adresse horizontale, et de les sérialiser grâce à un registre à décalage pour former le signal vidéo. La mémoire est donc organisée en mots:

Il est nécessaire de disposer d'une horloge tournant à la fréquence de succession des points, pour décaler le registre. La fréquence de modification des adresses mémoire et du signal de chargement du registre à décalage doit, elle, être n fois plus faible (si n est le nombre de bits du registre à décalage).

Changer la définition horizontale de l'image peut alors se faire de 2 façons différentes:

-on peut conserver le même registre à décalage et le même diviseur, et changer la fréquence de l'horloge "points". Il faut alors changer le fonctionnement du système de visualisation car le nombre de périodes par ligne TV sera différent.

on peut aussi changer la longueur du registre à décalage et le facteur de division du compteur proportionnellement à la définition horizontale, ce qui laisse constante la fréquence de fonctionnement du système de visualisation et le nombre de périodes par lignes.

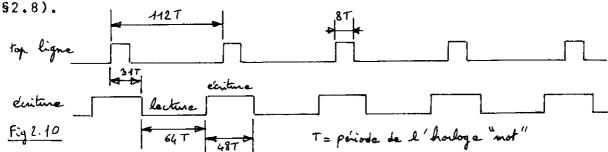

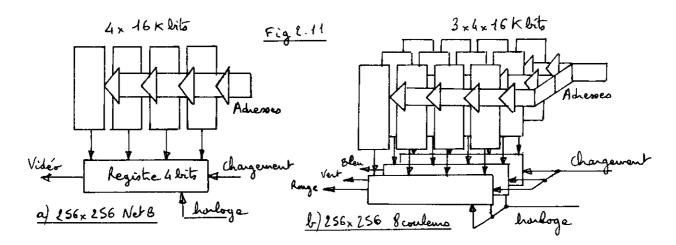

Nous avons choisi la deuxième solution, en excluant du circuit intégré la mémoire, le registre à décalage, le diviseur, et l'horloge points, ce qui rend le circuit très peu dépendant du format de visualisation, tout en permettant des applications comprenant peu de boîtiers (Fig.2.15 à 2.18).

La fréquence de fonctionnement du circuit, qui est aussi celle des accès mémoire, est choisie la plus élevée possible compte tenu de la technologie de réalisation (1,75MHz, ce qui correspond à 550ns de cycle). Comme cette fréquence est aussi celle d'accès à un point en écriture, ceci garantit une vitesse de tracé de nouvelles figures maximale (vecteurs, caractères). Le nombre de périodes de visualisation est 64 par lignes, ce qui en laisse 48 pour l'écriture. La fréquence d'écriture est donc de  $1,75 \times \frac{48}{112}$  MHz (environ  $1,3 \mu s/point$ ), et peut atteindre 1,75 MHz si on "force en écriture" (voir broche FECR

L'organisation de la mémoire en fonction du format est la suivante:

| <u>Définition:</u> | <u>n</u> : | <u>nécessaires:</u>      |    | organisation: |    |   | on:  |

|--------------------|------------|--------------------------|----|---------------|----|---|------|

| 512 <b>x</b> 512   | 8          | 16x16Kbits               | 32 | Kmots         | de | 8 | bits |

| 256 <b>x</b> 256   | 4          | 4x16Kbits                | 16 | Kmots         | de | 4 | bits |

| 128x128            | 2          | {4x 4Kbits<br>{2x 8Kbits | 8  | Kmots         | de | 2 | bits |

| 64 <b>x</b> 64     | 1          | lx 4Kbits                | ц  | Kmots         | de | 1 | bit. |

Pour augmenter le nombre de bits nécessaires pour décrire un point (couleurs, dégradés, superpositions), l'ensemble mémoireregistre doit être multiplié par ce nombre de bits. Mais la longueur

des mots mémoire et leur nombre restent constants. Il faut considérer que la mémoire croît dans une troisième dimension:

Pour une application avec niveaux de gris, les 3 sorties série commandent un convertisseur digital-analogique 3 bits. Pour une superposition, on utilise un OU logique.

#### 2.4-SELECTION DES BOITIERS MEMOIRE

Ce mode d'adressage de la mémoire ne suffit pas. En effet, en écriture, le générateur interne de vecteurs et de caractères accède les points un par un. Il faut donc utiliser la partie basse de l'adresse horizontale d'écriture pour choisir le bit concerné dans le mot mémoire. Comment notifier cette sélection de boîtier à l'extérieur du circuit intégré, alors que le nombre de boîtiers mémoire change suivant le format? (Fig. 2.15 à 2.18)

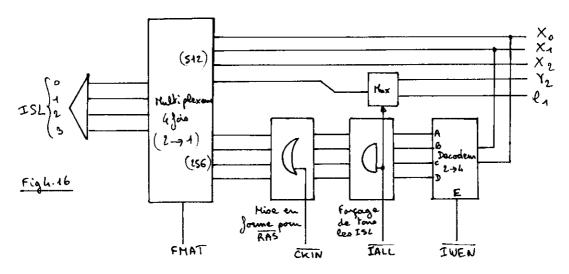

Considéront pour simplifier, uniquement les formats 512x512 (16 boîtiers) et 256x256 (4 boîtiers). Il est exclu de mobiliser 16 broches du circuit intégré pour cette sélection. Nous avons choisi de n'utiliser que 4 broches, l'adresse faible horizontale (sur 4 bits) sortant directement pour le format 512x512, et décodée pour le format 256x256 (en forme de RAS pour les connecter directement aux boîtiers). La fonction de ces 4 broches (appellées ISLO,1,2,3) dépend d'une

entrée (FMAT) spécifiant en outre au générateur de synchronisation s'il doit fonctionner de façon entrelacée ou non.

En 512x512, il faut donc adjoindre un décodeur extérieur.

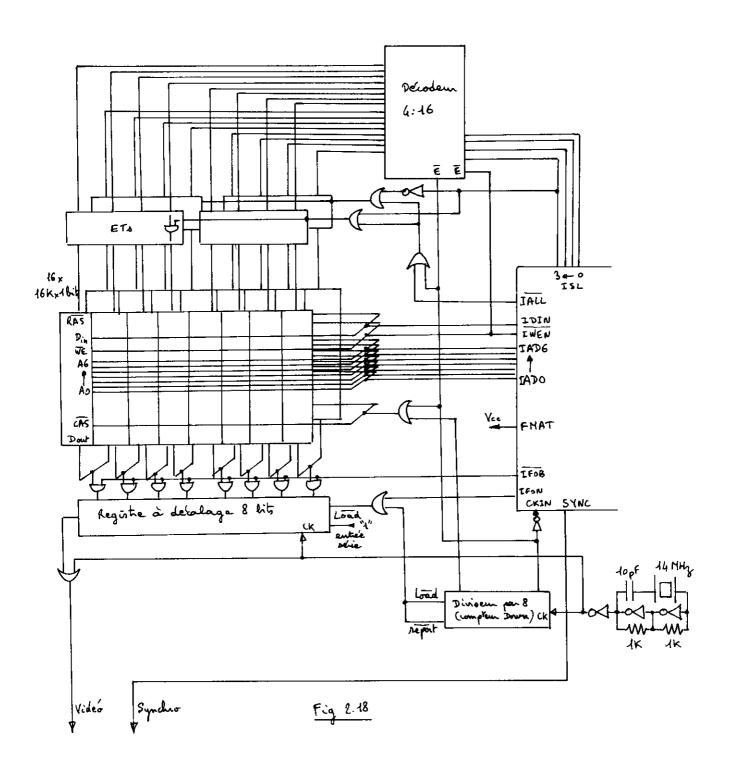

Pour la lecture, il est nécessaire de sélecter ensemble tous les bits d'un mot. En 256x256, les signaux de sélection ISLi s'en chargent. En 512x512, un signal supplémentaire (TALL) indique les phases de lecture et doit forcer la moitié des sorties du décodeur au niveau bas (Fig.2.18).

Dans les 2 formats, la portion visualisée de l'espace logique adressable est différente, mais la précision de visualisation est la même que la précision logique utilisée pour décrire les dessins (voir §2.10).

Considérons maintenant le cas des formats inférieurs à 256x256. Comme la synchronisation est identique au cas 256x256, la patte d'entrée FMAT doît être au même niveau logique. Les sorties ISLi sont regroupées 2 par 2 en 128x128 et les 4 ensemble en 64x64 (dans ce cas d'ailleurs les signaux ISLi sont inutiles, voir Fig.2.15). De la même façon, l'adressage vertical se fait en ignorant 1 bit en 128x128 puis deux en 64x64 (Fig.2.16). La précision de visualisation n'est plus la précision logique. Par exemple, un point de l'image 128x128 est le OU logique de 4 points de l'image 256x256.

Pour résumer, on peut dire que dans le format 256x256 (et inférieurs), l'adresse de point est constituée de 16 bits dont 2 sont décodés sur ISLi, et les 14 autres envoyés en deux coups sur IADi. Dans le format 512x512, l'adresse comprend 18 bits dont 4 sont envoyés sur ISLi, et les 14 autres sur IADi.

### 2.5-SIGNAUX DE CONTROLE MEMOIRE

Les adresses sont envoyées en 2 coups, conformément aux

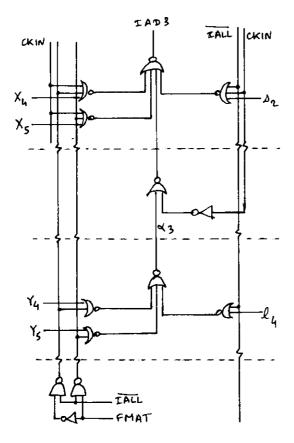

spécifications des mémoires. Elles sont donc issues d'un multiplexeur à 8 entées, commandé par 3 signaux:

- -FMAT.

- -lecture/écriture (= IALL),

- -partie haute/partie basse.

Le signal FMAT est nécessaire au niveau de ce multiplexeur, d'une part pour changer la partie de l'espace adressable mémorisée, et surtout pour adapter au rafraîchissement des mémoires (voir schémas d'applications, Fig. 2.15 à 2.18).

Le signal de commutation entre partie haute et partie basse est le signal d'horloge du boîtier (broche CKIN). La modification du rapport cyclique de celui-ci entraîne la modification de l'instant de commutation entre ces adresses. Ceci permet d'utiliser toutes les mémoires ayant un temps de cycle inférieur à la période de fonctionnement du circuit intégré (550ns).

Le signal IALL est bas lors des phases de lecture ou de rafraîchissement. Il est identique à toutes les lignes et peut être utilisé comme signal de cadrage horizontal. Le circuit intégré commande en outre le signal d'écriture WE des mémoires (broche IWEN) -ce signal n'est bas que pour les périodes d'écriture effective dans la mémoire-, ainsi que la donnée d'entrée des mémoires (broche IDIN) qui change en fonction d'un bit du mot de contrôle (voir \$2.10) et peut aussi être forcée lors d'un cycle d'effacement. Ce signal sur l bit n'est pas particulier à la visualisation en Noir et Blanc. En effet, dans les visualisations en couleurs par exemple, un des états des points est particulier: l'état "éteint". La sortie IDIN doit être considérée comme une sortie de forçage de la donnée mémoire à l'état éteint (actif haut).

Il faut ajouter à ces signaux deux sorties pour forcer à volonté le signal vidéo dans un état déterminé. Ce sont le forçage à noir (IFON) et le forçage à blanc (IFOB). IFON sert à nettoyer le signal vidéo sur les bords de l'écran ("blanking"), quand les sorties des mémoires peuvent présenter des états indésirables (rafraîchissement, écriture). Ceci permet d'ailleurs d'adapter toutes sortes de mémoires, même à entrées-sorties multiplexées. IFOB sert au début de chaque trame dans la partie non visible de l'écran, pour forcer le signal vidéo à blanc pendant une ligne, conformément aux normes. Il permet en outre de forcer l'écran à blanc pour simplifier l' utilisation du "Light pen" (§2.13).

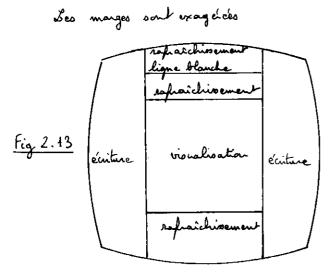

Note: occupation de l'écran: la zone de rafraîchissement (qui ne se distingue de celle de visualisation que par le niveau haut du signal IFON) est indispensable. Elle ne peut pas par exemple être intégralement transformée en écriture. En effet, le temps correspondant aux marges haute et basse est de l'ordre de 64x(312-256)µs±3,5ms ce qui est trop long sans rafraîchissement (max:2ms).

La ligne blanche en haut a lieu pendant le temps de forçage à noir.

Or, il est plus facile (voir Fig. 2.15 à 2.18) de réaliser un forçage à noir prioritaire sur le forçage à blanc que l'inverse. Pour cette raison, IFON devient bas lors de cette ligne. Dans ces conditions, les forçages à blanc et à noir sont

toujours exclusifs et tous les montages extérieurs concernant ces signaux sont possibles.

## 2.6-EXEMPLES DE MONTAGES (NOIR ET BLANC)

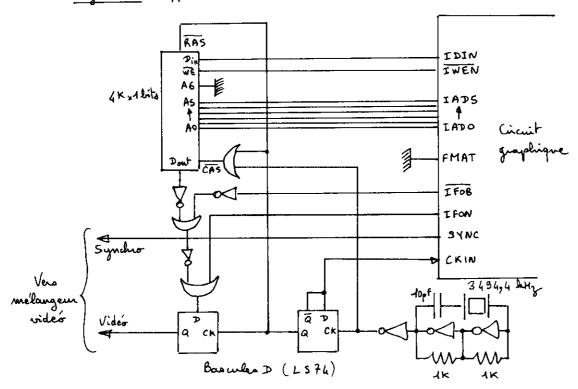

- a)64x64. Un seul boîtier 4Kxl bits suffit. Les bits sont accédés séquentiellement le long d'une ligne. Chaque ligne est répétée 4 fois. Il est nécessaire de disposer d'une horloge au double de la fréquence point pour générer CAS. La sortie de la mémoire n'étant pas toujours valide, une bascule est nécessaire. Dans cette application, nous obtenons un affichage graphique 64x64 N&B en 5 boîtiers (Fig.2.15).

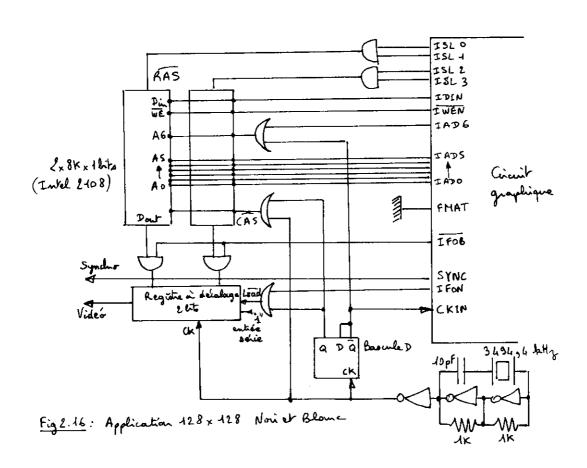

- b)128x128. Il faut 2 boîtiers de 8Kbits (INTEL 2108 par ex.), ou 4 boîtiers de 4Kbits. IAD6 n'est utilisé que pour sa partie basse.

Fig 2.15: Application 64x64 Novi et Blanc

Une horloge à la fréquence point décale le registre et permet de générer CAS. IFON intervient en empêchant le chargement du registre. Dans ces conditions, il y a bien forçage à noir si l'entrée série du registre est au niveau haut. On peut utiliser une seule mémoire 16K si elle a un temps de cycle inférieur à 275 ns. On fait alors des accès à la fréquence points. L'adresse supplémentaire est fournie en écriture par les ISL, et en lecture par le diviseur extérieur.

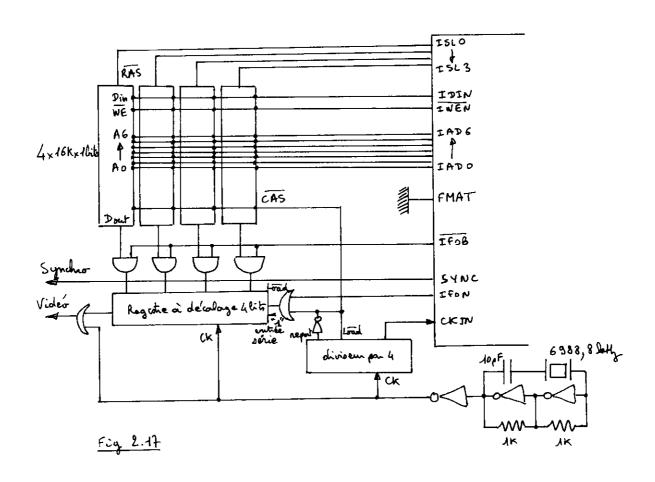

c)256x256. On utilise 4 boîtiers 16Kbits.

d)512x512. Les 4 sorties ISLi doivent être décodées pour commander les 16 mémoires 16K. Celles-ci sont arrangées en 2 moitiés de 8 boîtiers. Lors de la lecture, une moitié entière est sélectée. Ceci se fait en conjuguant IALL et ISL3 qui porte alors une adresse de visualisation.

L'ensemble de toutes les cases mémoire est lu sur 2 trames TV.

La séparation des lignes TV suivant leur parité ne coîncide pas avec la séparation en 2 moitiés, sinon une moitié ne serait pas rafraîchie pendant une trame. Il y a basculement de la moitié utilisée toutes les 2 lignes d'une même trame(grâce à la sortie ISL3), soit tous les 128 accès.

e)<u>Autres formats</u>. Vu le mode de sélection des boîtiers par les sorties ISL, il n'est pas possible d'avoir un format dont le nombre de colonnes ne soit pas une puissance de 2. De même, il est difficile d'utiliser le boîtier pour une définition verticale qui ne soit pas non plus une puissance de 2.

Par contre, il n'est pas obligatoire d'avoir des définitions horizontale et verticale égales, mais cela présente peu d'intérêt. Des définitions égales ne signifient pas un écran carré. On peut en effet régler les amplificateurs de déviation du moniteur pour déformer l'image. Mais alors, une composante des vecteurs et des caractères devra subir une homothétie software pour corriger la déformation du dessin.

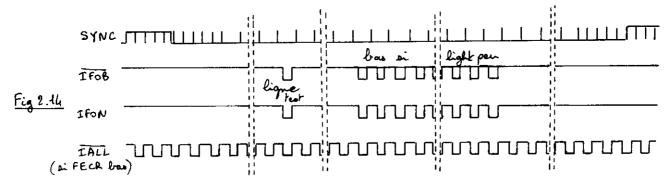

### 2.7-SIGNAL DE SYNCHRONISATION

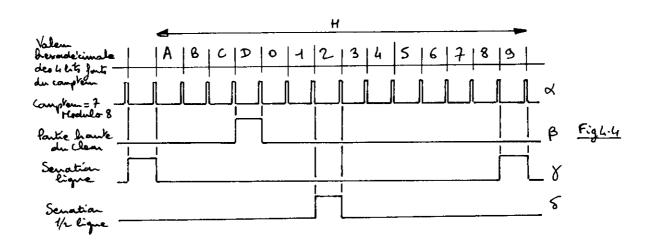

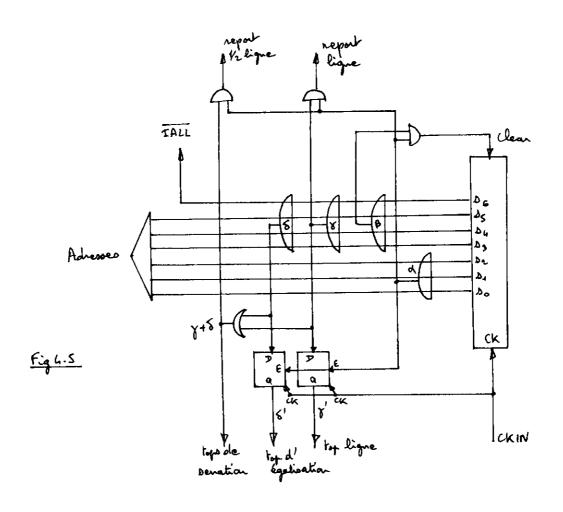

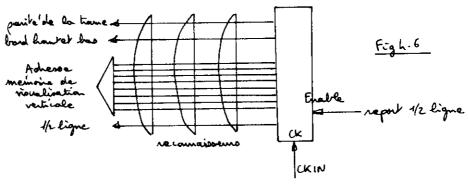

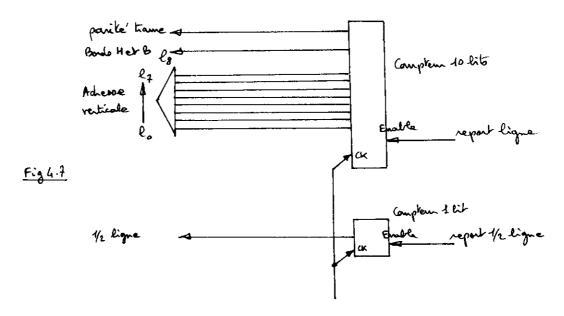

Il est généré sur la sortie SYNC. Sa forme est celle de la figure 2.5, la durée des paliers étant 8T ou 112-8=104T, si T est la période de l'horloge CKIN. Ce signal ne change d'état que sur un front descendant de CKIN puisqu'il est généré à partir de reconnaisseurs sur le compteur de visualisation. Dans le cas où FMAT est bas, tous les tops trames sont ceux de la figure 2.5.b.

Ce circuit peut facilement synchroniser une autre source de signal vidéo puisque les signaux de cadrage peuvent se déduire de SYNC, IALL, IFOB, et IFON. Par contre, il ne comprend pas les fonctions nécessaires pour se synchroniser lui-même sur une autre source. Toutefois, il est possible de le faire en agissant sur l'horloge CKIN qui peut très bien voir l'une quelconque de ses phases s'allonger.

### 2.8-RECAPITULATION DE LA PARTIE VISUALISATION

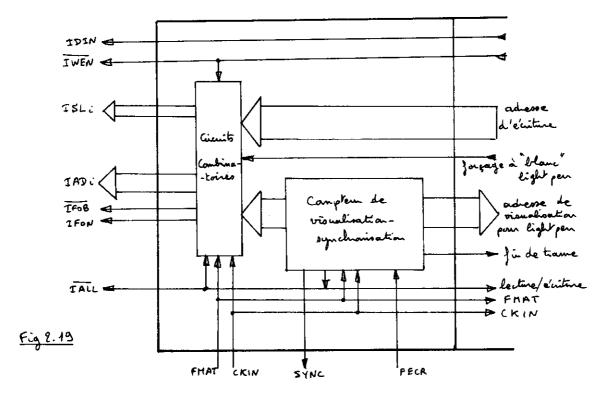

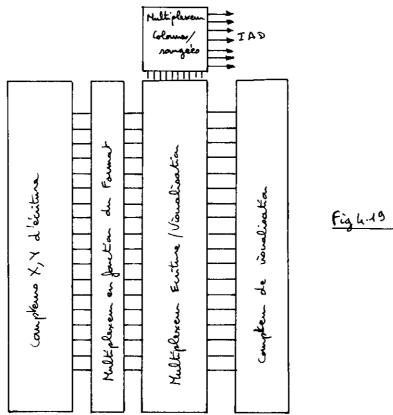

On peut représenter toute la partie lecture-synchronisationgestion mémoire de la façon suivante:

Tous les signaux à droite sont des signaux d'échange avec la circuiterie d'écriture. L'entrée FECR ("forçage en écriture") supprime toutes les phases de visualisation, et laisse 112 périodes par ligne pour l'écriture. IFON et TALL sont alors toujours à l'état haut.

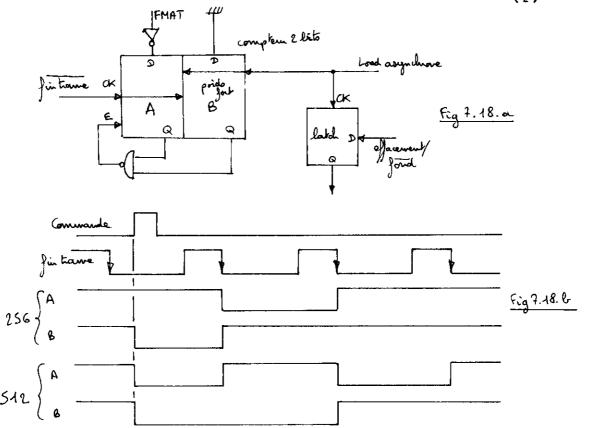

Le signal "fin trame" est haut de la dernière ligne visualisée d'une trame à la première ligne de la trame suivante. Il est utilisé par le système d'écriture dans la gestion du light-pen, de l'effacement de l'image, et peut être la cause d'une interruption (§2.15).

#### 2.9-SYSTEME D'ECRITURE

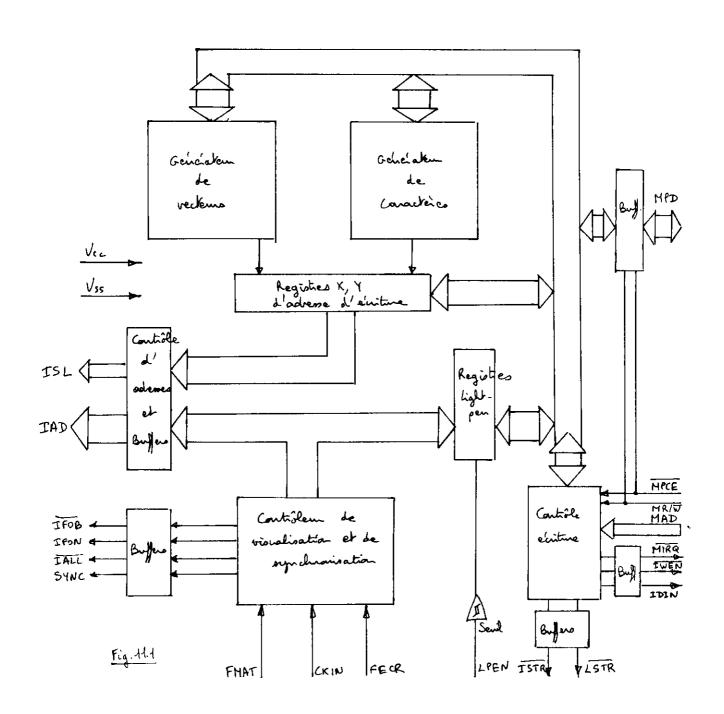

Cette partie du circuit doit être considérée comme une interface entre la partie visualisation et le bus microprocesseur.

Elle est entièrement sous le contrôle de la visualisation par les signaux CKIN et TALL. Son rôle est de fournir à chaque cycle mémoire d'écriture une adresse et le signal TWEN.

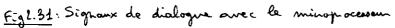

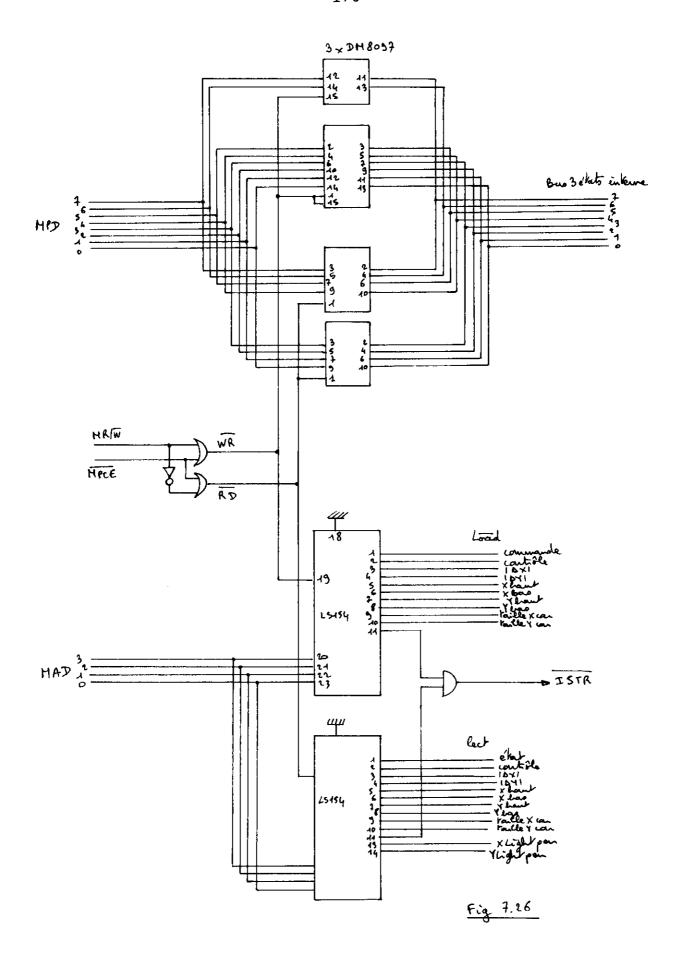

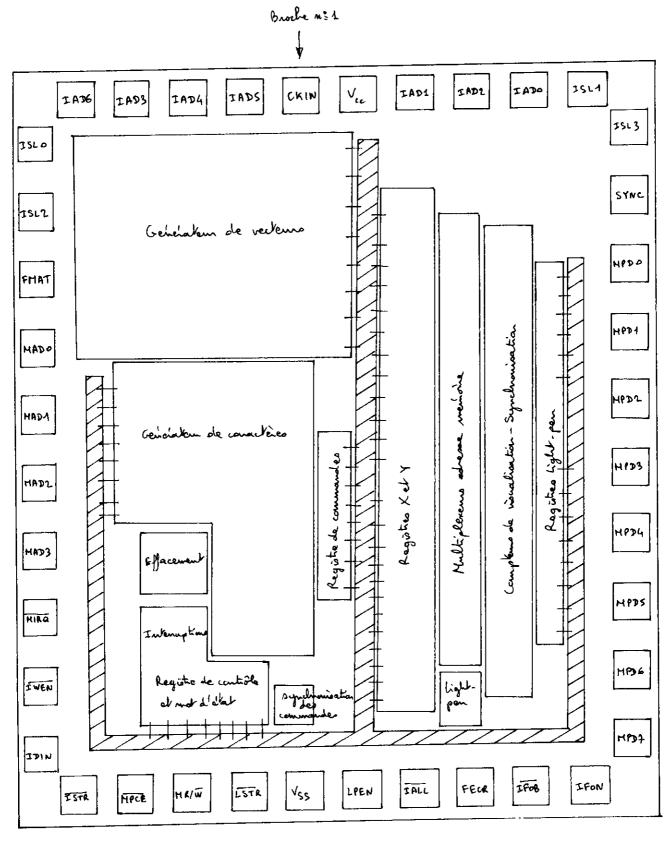

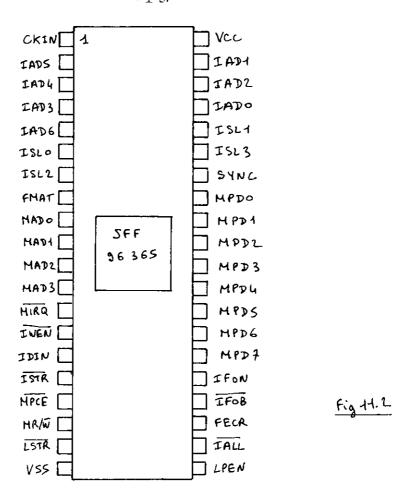

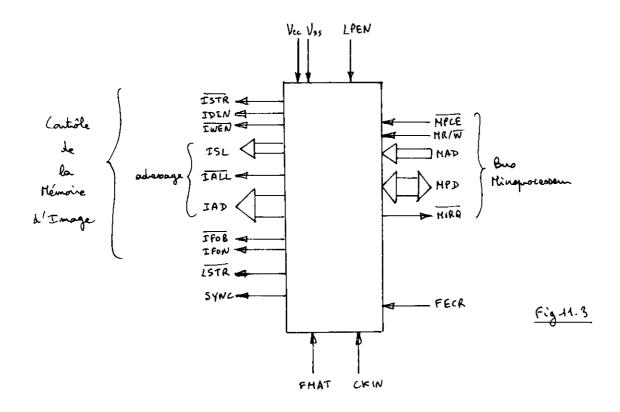

Du côté bus microprocesseur, elle simule une suite de 13 cases mémoires qui peuvent être accédées par le microprocesseur en lecture ou en écriture à l'aide d'un bus de données bidirectionnel de 8 bits (MPDi) et d'un bus d'adresse de 4 bits (MADi). Les échanges sont contrôlés par un signal temporel (MPCE) et un signal de lecture/écriture (MR/W). Certaines cases correspondent à des registres internes (tel que l'adresse d'écriture X,Y par exemple). D'autres cases n'ont pas la même signification en lecture et en écriture. La case 0 par exemple est l'endroit où l'on écrit les commandes, et où on peut lire le mot d'état. La description précise de ces registres est donnée \$2.18. (voir aussi figure 11.1)

### 2.10-REGISTRES X ET Y

L'adresse d'écriture est constituée de 2 registres de 12 bits chacun: X et Y. Ils permettent donc d'adresser un espace de 4096x4096 points. Ils donnent en permanence l'adresse où pourrait s'effectuer une écriture en mémoire, équivalente à l'adresse du "spot" d'une visu à balayage cavalier. Cette adresse d'écriture peut être modifiée (ce spot peut être déplacé) de 2 façons: ou bien on la fixe de manière absolue par un chargement des registres X,Y; ou bien on utilise le générateur de vecteurs et de caractères qui au cours d'un traçage incrémente ou décrémente les registres X ou Y. Ces 2 registres de 12

bits sont chacun découpés en une partie basse de 8 bits et une partie haute de 4 bits. Cette dernière est étendue à 8 bits avec des zéros placés devant. Ce découpage permet leur accès par le bus 8 bits du microprocesseur (adresses 4,5,6,7). (voir tableau 2.1)

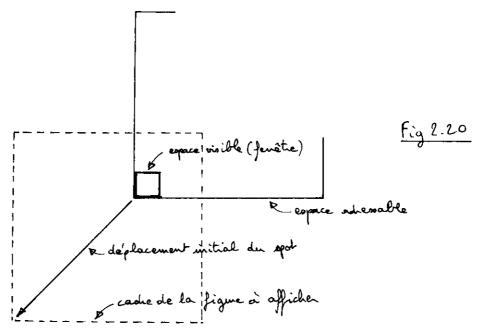

Parmi les 4096x4096 points adressables, seule une fenêtre est visualisée et réellement mémorisée. Si le spot est en dehors de cette fenêtre, l'écriture est inhibée (signal TWEN forcé haut). L'espace adressable est cyclique, c'est-à-dire que si le spot dépasse sur un bord, il apparaît sur le bord opposé. Ceci, associé à une description relative des vecteurs (par leurs projections ΔX et ΔY) et des caractères, permet de résoudre automatiquement la plupart des problèmes de découpage d'une fenêtre dans une figure. Toute portion d'une grande figure 4096x4096 est visualisable. Il suffit de déplacer initiallement, non pas la fenêtre, mais la grande figure par un seul positionnement du spot. Comme tous les éléments sont définis de façon relative, la figure sera globalement translatée:

Néanmoins, il est possible de restreindre l'espace cyclique à celui de la fenêtre, en positionnant le bit de poids fort du registre de contrôle (adresse l -voir tableau 2.1). Quelquesoit la valeur de ce bit, il est en outre possible de savoir si l'adresse (complète)

d'écriture correspond à un spot hors de la fenêtre ou non (bit 3 du mot d'état). Il est à noter que cette dernière information est fonction de l'entrée FMAT.

Indépendemment de la position du spot, celui-ci peut être "allumé" ou "éteint" (s'il est éteint, le signal TWEN est toujours haut). Il peut aussi être "marquant" ou "effaçant" (cette caractéristique commande la sortie IDIN). Ces 2 caractères sont contrôlés par les bits 2 et 3 du mot de contrôle.

### 2.11-GENERATEUR DE VECTEURS

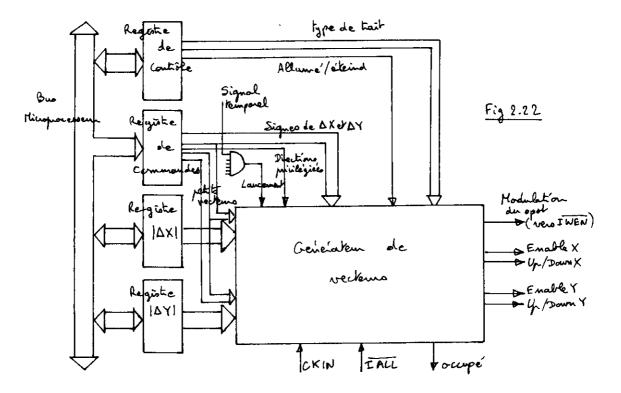

C'est un automate qui reçoit en entrée les projections du vecteur  $\Delta X$  et  $\Delta Y$ , et qui génère en sortie des incréments (ou décréments) pour les registres X et Y.

On spécifie séparément  $|\Delta X|$ ,  $|\Delta Y|$  et les signes associés.  $|\Delta X|$  et  $|\Delta Y|$  sont 2 registres de 8 bits accessibles par le bus microprocesseur (adresses 2 et 3), ce qui impose:

$$\begin{cases}

-255 \leqslant \Delta X \leqslant 255 \\

-255 \leqslant \Delta Y \leqslant 255.

\end{cases}$$

Les signes (et nullités éventuelles) sont spécifiés par les 3 bits de poids faibles d'un octet de commande de la façon suivante: (codes de commande H'10' à H'17' )

bits faibles:

000

$$\Delta X \geqslant 0$$

;  $\Delta Y = 0$

001  $\Delta X \geqslant 0$ ;  $\Delta Y \gg 0$

010  $\Delta X = 0$ ;  $\Delta Y \geqslant 0$

011  $\Delta X \leqslant 0$ ;  $\Delta Y \geqslant 0$

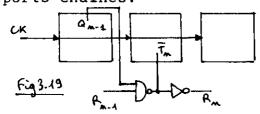

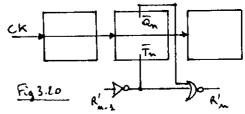

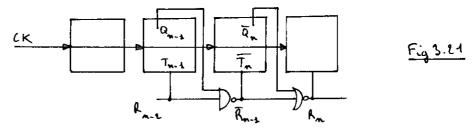

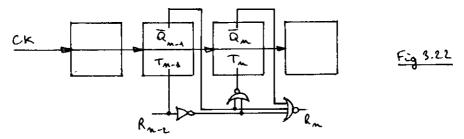

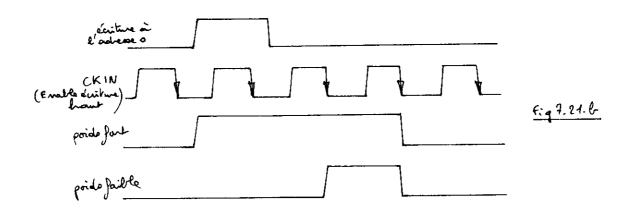

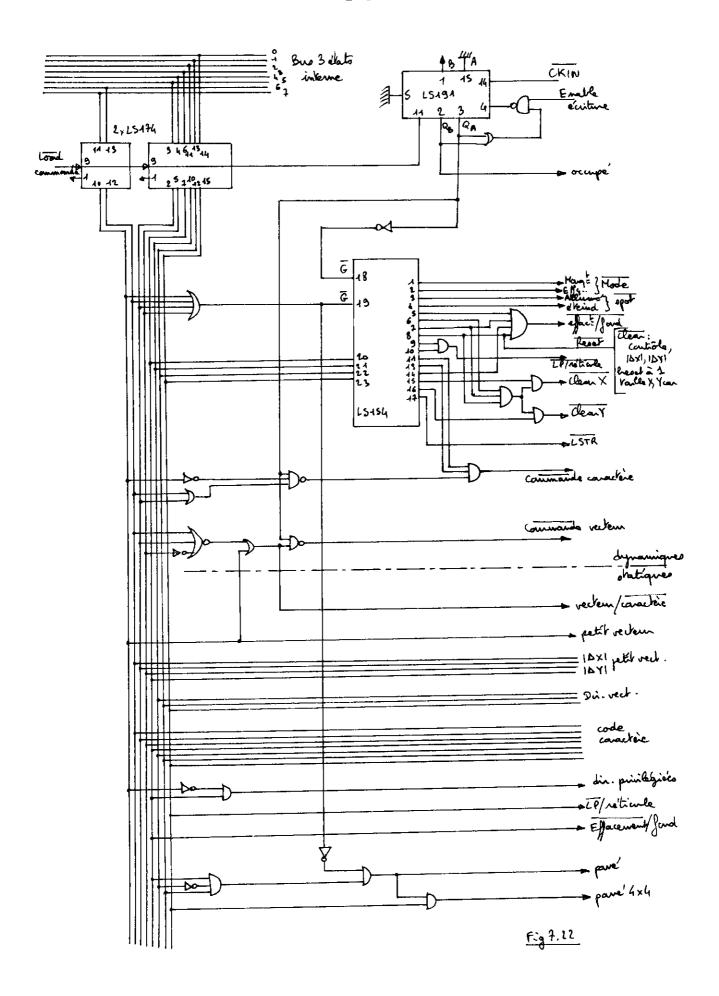

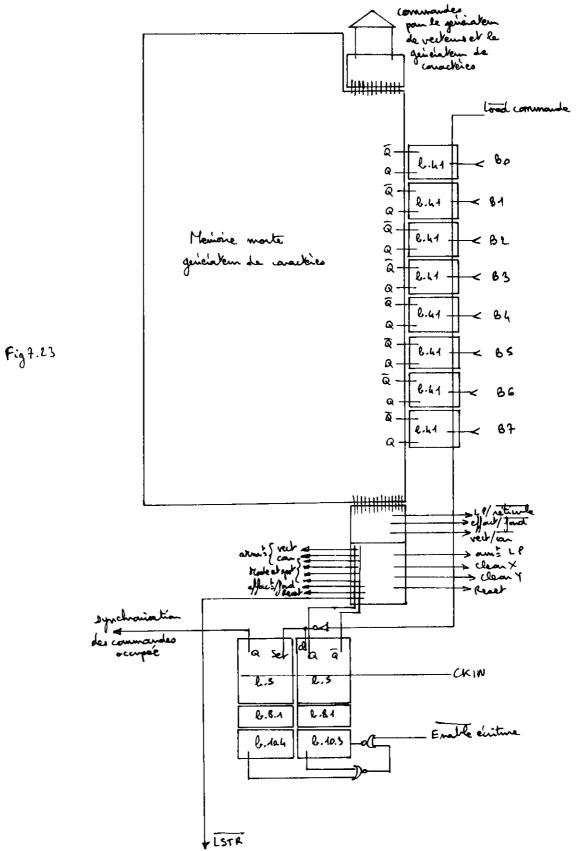

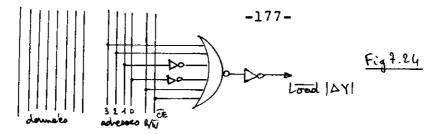

100  $\Delta x \leqslant 0$ ;  $\Delta Y = 0$  Fix  $9.21$

<sup>+</sup> H est mis pour hexadécimal.

| 101 | $\Delta X \leq 0; \Delta Y \leq 0$                                                   |

|-----|--------------------------------------------------------------------------------------|

| 110 | $\Delta X = 0; \Delta Y \leqslant 0$<br>$\Delta X \geqslant 0; \Delta Y \leqslant 0$ |

| 111 | ∆x > 0; ∆ Y ≤ 0                                                                      |

Ceci permet de tracer de nombreuses figures géométriques simples en changeant peu souvent les registres  $|\Delta X|$  et  $|\Delta Y|$ , et donc à raison de l octet par vecteur. Pour le cas où les vecteurs tracés sont parallèles aux axes ou aux bissectrices, des codes de commande spéciaux (H'18' à H'1F') permettant de ne tenir compte que d'un seul registre  $|\Delta X|$  ou  $|\Delta Y|$ . Les projections des vecteurs sont alors choisies égales dans les 2 directions à:

$|\Delta X| = |\Delta Y| = \sup(\text{registre} |\Delta X|, \text{ registre} |\Delta Y|)$

Les signes et nullités sont spécifiés de la même façon que pour les autres vecteurs.

Remarque: dans le cas  $|\Delta X|$  = 50 et  $|\Delta Y|$  = 100, le code de commande H'18' (direction 0) trace le vecteur:

Ces codes sont nommés "Directions privilégiées" dans le tableau 2.2.

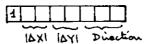

Pour les cas de tracés de petits vecteurs ( $|\Delta X| \le 3$  et  $|\Delta Y| \le 3$ ), des codes de commande spéciaux (H'80' à H'FF') spécifient en un seul octet  $\Delta X$  et  $\Delta Y$  d'après le format suivant:

et sans changer les registres  $|\Delta X|$  et  $|\Delta Y|$  qui peuvent être utilisés conjointement pour de grands vecteurs. Tous ces codes spéciaux permettent de minimiser l'information nécessaire pour décrire une image composée de traits.

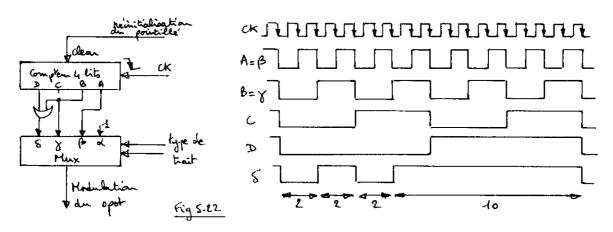

Les vecteurs peuvent être tracés de 4 types de traits différents spécifiés par les 2 bits de poids faibles du registre de contrôle: trait continu, trait pointillé (1 point allumé, 1 point éteind), trait tireté (2 points allumés, 2 points éteinds), et trait mixte

(10 points allumés, 2 éteinds, 2 allumés, 2 éteinds). Le circuit générant les traits non continus est toujours positionné de la même façon pour un vecteur donné au départ du traçage. Ceci garantit que l'effacement d'un vecteur non continu puisse s'obtenir en ne changeant que la bascule Marquant/Effaçant, à condition toutefois que le vecteur soit parcouru dans le même sens qu'au traçage.

Lors d'un tracé, le générateur fait passer le spot de l'adresse  $(X_o,Y_o)$  à l'adresse  $(X_o+\Delta X,Y_o+\Delta Y)$ . Le temps moyen de tracé est environ  $1,3(m+3)\mu s$  (si m est  $\sup(|\Delta X|,|\Delta Y|)$ ) ou  $0,55(m+3)\mu s$  si on utilise le forçage en écriture (broche FECR). Le nombre d'accès mémoire pour ce tracé est m+1, car les points origine et extrémité sont inscrits. Ainsi, si le spot est allumé, le traçage d'un vecteur pour lequel  $\Delta X=\Delta Y=0$  a pour effet de marquer le point où se trouve le spot.

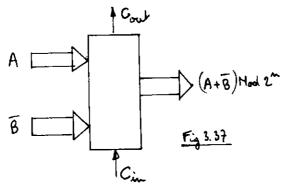

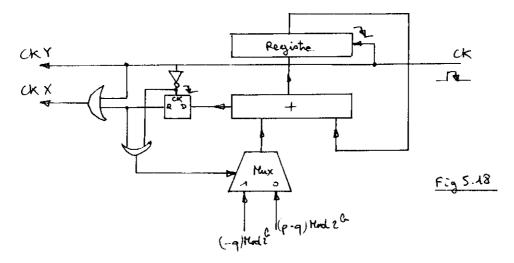

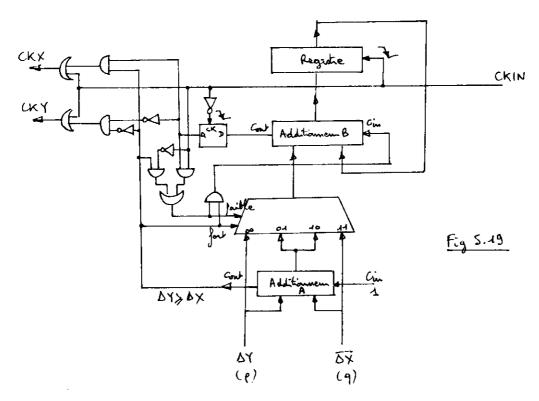

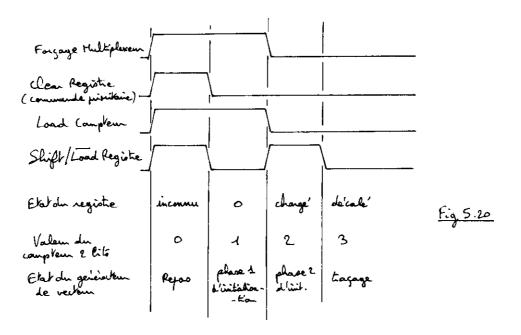

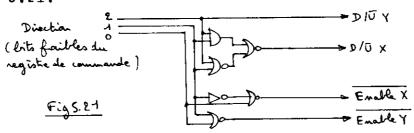

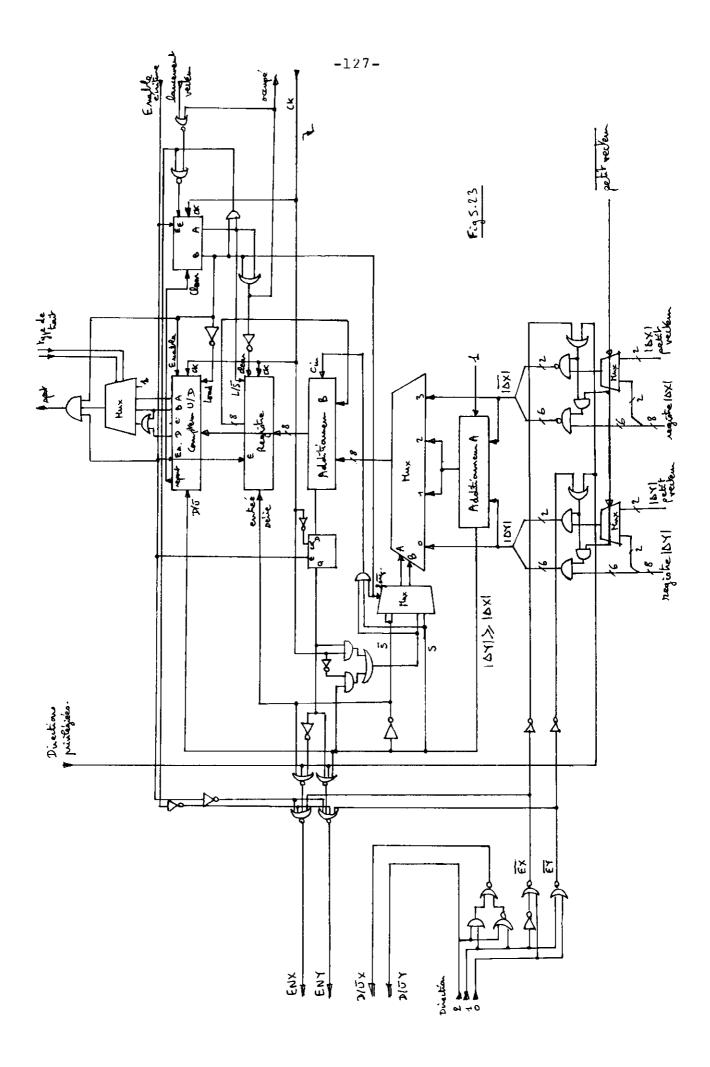

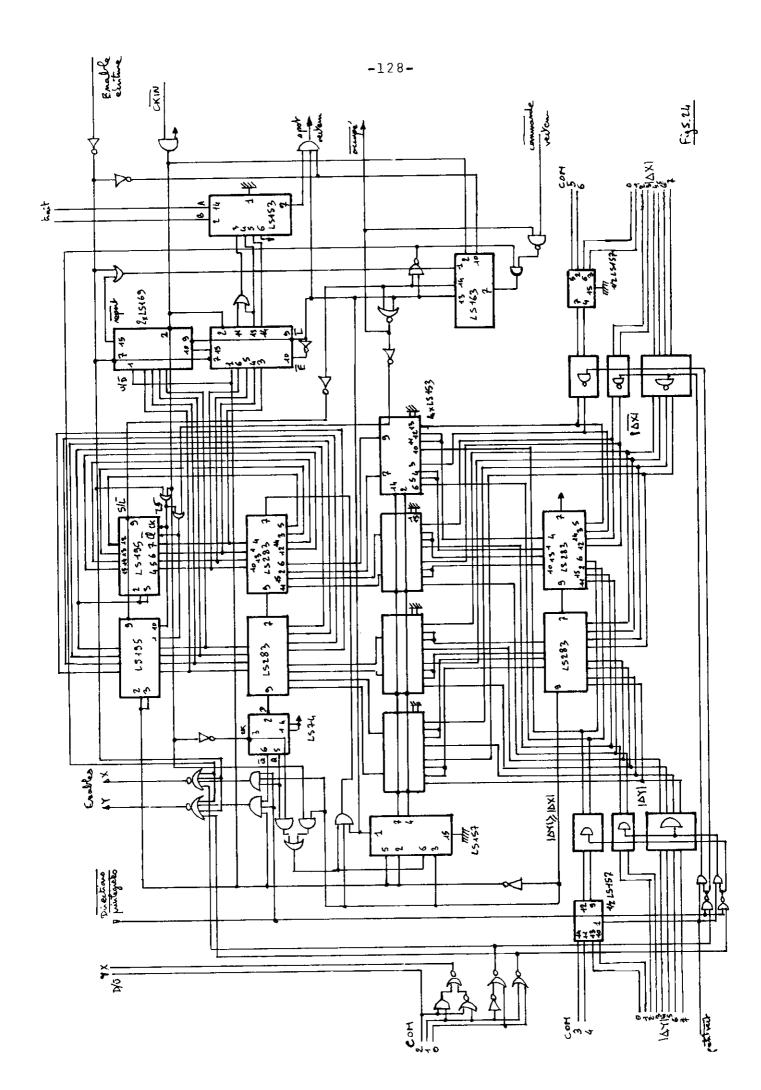

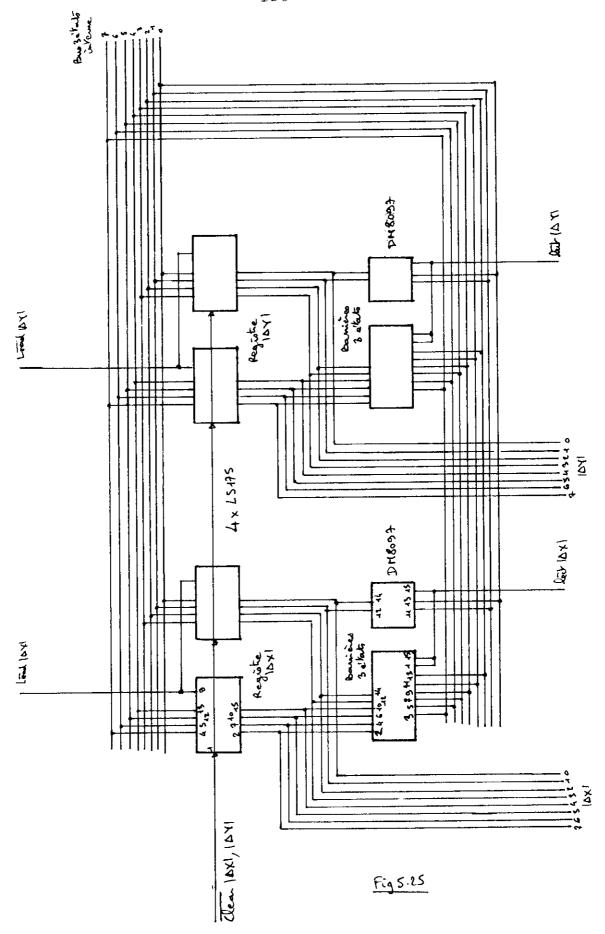

Le générateur de vecteurs peut se symboliser ainsi:

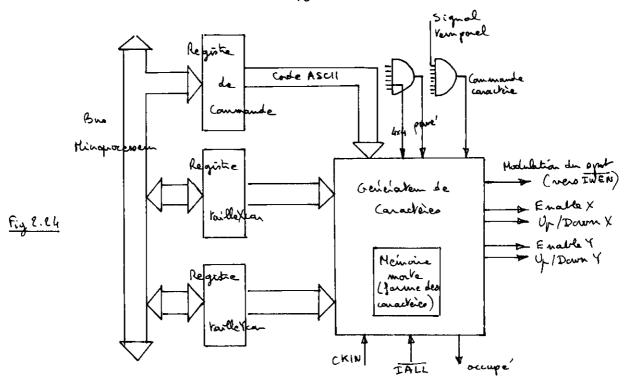

### 2.12-GENERATEUR DE CARACTERES

Le générateur de caractères est comparable au générateur de

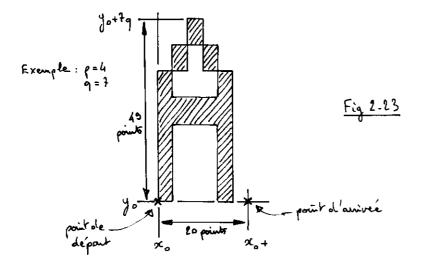

vecteurs en ce qui concerne son branchement. Il génère des incréments et des décréments pour X et Y. Ses entrées sont d'une part le code du caractère à tracer (parmi les 95 caractères full-ASCII imprimables), et d'autre part 2 facteurs d'homothétie à appliquer à ce caractère suivant x et suivant y. Ces 2 facteurs peuvent varier indépendemment et de l à 16. Les caractères sont tracés à partir d'une matrice 5x7, et l'espace entre 2 caractères est de l colonne. Le spot lors du traçage passe de  $(X_o, Y_o)$  à  $(X_o+6p, Y_o)$ . Ceci permet de tracer jusqu'à 64 lignes de 85 caractères (dans le format 512x512).

A partir du même générateur, on peut tracer des "pavés" de 2 sortes:

-un pavé de 5px7q points allumés qui permet aussi d'effacer tout caractère,

-un pavé de 4px4q points pour lequel le spot passe de  $(X_o, Y_o)$  à  $(X_o+4p, Y_o)$ .

Les facteurs p et q sont accessibles par le bus microprocesseur où ils se nomment "tailleXcar" et "tailleYcar" (adresses H'8' et H'9'). Ils sont constitués de 4 bits étendus à 8 avec des zéros placés devant. La valeur H'00' donne un facteur égal à 16. Les quatre bits forts sont toujours ignorés en écriture, nuls en lecture.

Le générateur de caractères peut se schématiser ainsi:

### 2.13-LIGHT-PEN ET RETICULE

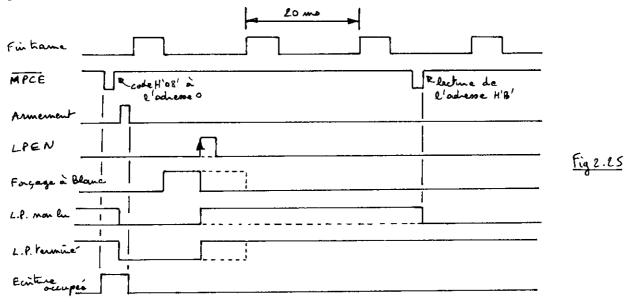

Si le circuit a reçu le code de commande "armement light-pen" (code H'08') ou "armement réticule" (H'09'), il attend lors de la trame suivante un front montant sur l'entrée LPEN qui sert à échantillonner la valeur courante de l'adresse de visualisation dans 2 registres "Xlight-pen" et "Ylight-pen". Ces registres sont accessibles en lecture seule sur le bus microprocesseur (adresses H'B' et H'C').

Dans le cas d'un armement light-pen, la vidéo est "forcée à blanc" (par la broche TFOB) lors de la trame considérée. Dans le cas du réticule, les traits sur l'image doivent être générés extérieurement au boîtier. Le OU logique des 2 signaux "trait vertical" et "trait horizontal" doit être envoyé sur la broche LPEN du circuit (Il est souvent préférable de dessiner le réticule par programme. Pour éviter d'effacer l'image, il peut être tracé par complémentation du contenu [10], en faisant fonctionner la mémoire en "Read-Modify-Write").

X light pen est l'adresse d'un mot de la mémoire d'image le long d'une ligne. Seuls ses 6 bits de poids forts sont significatifs.

En format 512x512, Xlight pen et Y light pen sont toujours cadrés sur un octet, comme en 256x256. Il faut alors les multiplier par 2 pour obtenir l'adresse logique réelle si nécessaire.

Il faut soustraire une quantité constante au registre Xlight pen pour compenser les retards introduits entre la sortie d'une adresse sur IADi et le signal LPEN. Ces retards dépendent du montage externe.

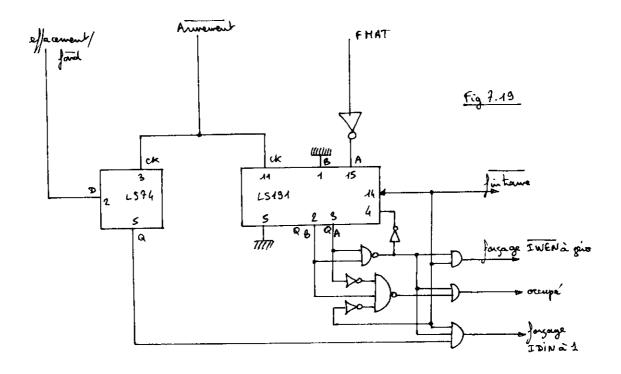

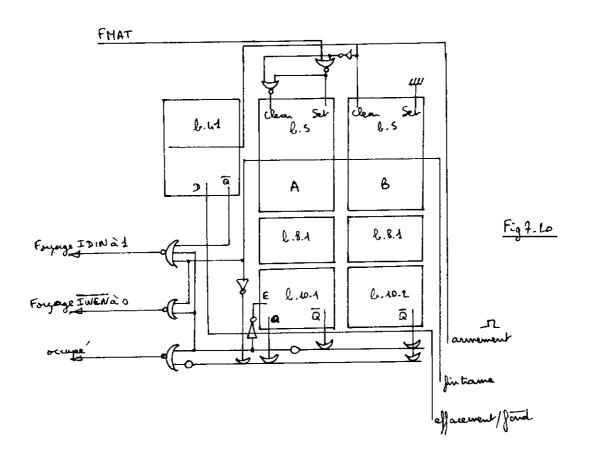

Les signaux internes de gestion du light pen sont représentés en figure 2.25. Dans le cas du réticule, la seule différence est l'abscence de "forçage à blanc".

Le signal "light pen non lu" est accessible en bit faible du registre X light pen. Il est remis à 0 par la lecture du registre X light pen ou de Y light pen. Le signal "light pen terminé" est accessible dans le mot d'état et peut être à l'origine d'une interruption.

# 2.14-MECANISME D'EFFACEMENT DE L'IMAGE ENTIERE

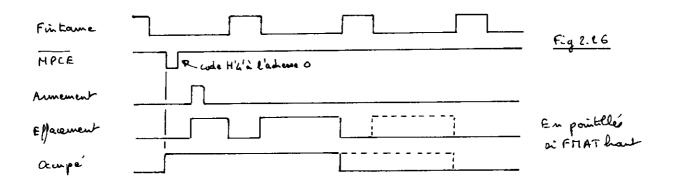

Pour effacer toute l'image, ou pour la positionner à un état particulier (fond non Noir), 2 codes spéciaux sont prévus (H'04' et

H'OC'). Ils agissent pendant les phases de visualisation. Le temps minimal nécessaire est donc une trame si FMAT est bas, 2 trames si FMAT est haut. Ces trames sont comptées à partir du front descendant de "fin trame" qui suit la commande. Les signaux de contrôle sont représentés en figure 2.26. Le signal effacement force TWEN bas. Dans le cas du code H'04', il force aussi IDIN haut. L'action de ces codes est indépendante des bits 2 et 3 du registre de contrôle, et ne les modifie pas.

Si les boîtiers mémoire sont montés pour fonctionner en "Read-Modify-Write" lors de la visualisation, la(les) trame(s) effaçante(s) sera(ont) visualisée(s). Ceci permet de faire du dessin animé à une vitesse maximale, en écrivant le nouveau dessin lorsque "fin trame" est haut, et en lançant l'effacement avant même le début de la trame. La visualisation effacera la mémoire, prête pour la trame suivante. Dans une telle utilisation, il peut être souhaitable d'augmenter la vitesse moyenne d'écriture pour augmenter le nombre de points inscriptibles lors de "fin trame". Ceci peut être obtenu par un montage permettant de commander l'entrée FECR par programme. Mais ceci est dangereux car supprime le rafraîchissement.

### 2.15-MECANISME D'INTERRUPTION

Trois signaux internes différents peuvent être à l'origine d'une

### interruption:

-"système d'écriture libre": Ce signal est le NOR de 4 signaux:

"générateur de vecteurs occupé", "générateur de caractères occupé",

"effacement occupé", et "analyseur de commandes occupé". Il doit être

testé avant l'envoi de toute commande pour ne pas perturber l'

exécution de la précédente.

-"fin trame": Ce signal peut servir d'horloge à 50Hz (dont la précision est liée à celle de l'horloge CKIN), ou mieux permet de synchroniser une modification de l'image avec le défilement des trames.

-"light pen terminé".

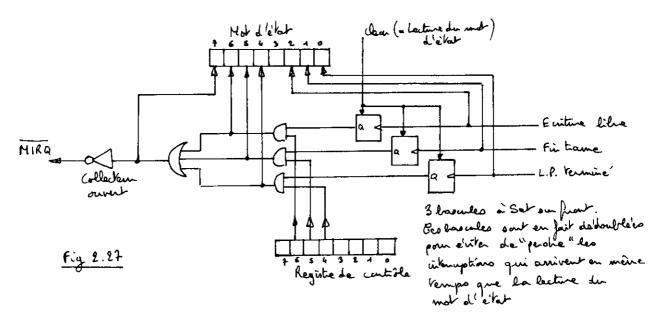

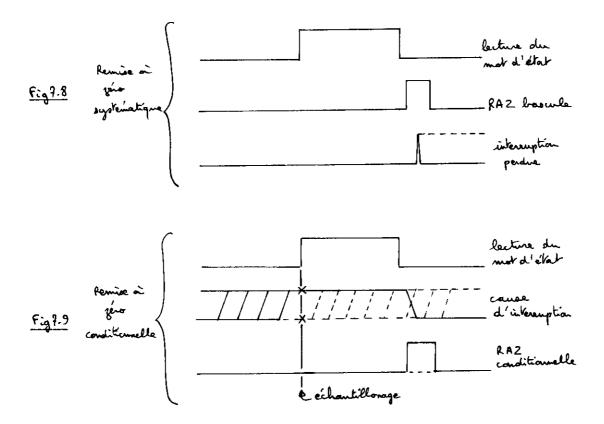

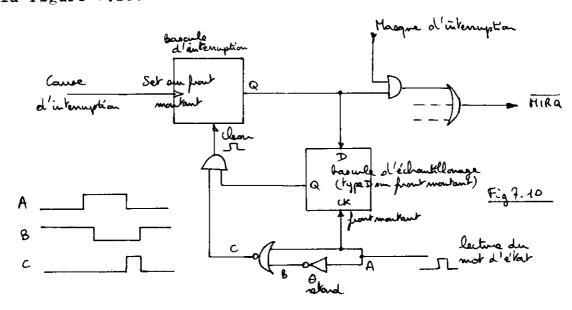

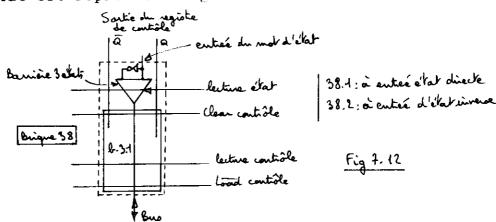

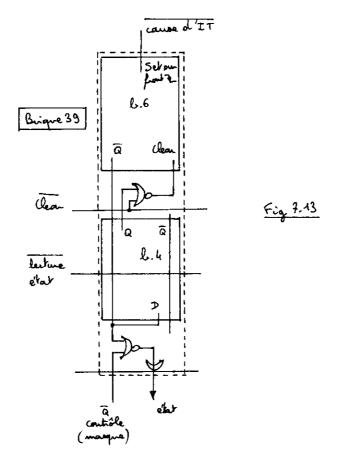

Le système de prise en compte des interruptions est le suivant:

### 2.16-LECTURE D'UN POINT DE LA MEMOIRE D'IMAGE

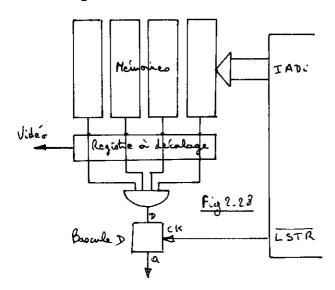

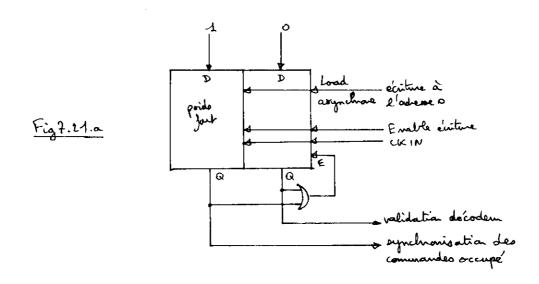

Cette commande (code H'OF') déclenche le mécanisme d'écriture au point adressé par X,Y sans modifier cette adresse. Mais, au moment de l'écriture, au lieu de baisser IWEN, le circuit baisse une autre sortie: LSTR. C'est donc une lecture à l'adresse X,Y qui a lieu. La sortie des mémoires lors de cette lecture peut être échantillonnée

par LSTR dans un registre accessible extérieurement par le microprocesseur. De cette manière, le programmeur peut travailler point par point dans la mémoire d'image. Suivant le montage, on recueille un mot entier (dont la longueur dépend de la configuration mémoire) si LSTR force IALL, ou un seul point si on se sert de la sélection par ISL (Fig. 2. 30 et 2.28 respectivement).

Exemple: lecture d'un point en 256x256 N&B. On a utilisé des mémoires dont la sortie est haute quand elles ne sont pas sélectées.

### 2.17-LIAISON AU BUS MICROPROCESSEUR

Les signaux d'échange avec le microprocesseur sont représentés Fig.2.31. Les adresses des registres et les codes de commande sont résumés dans les tableaux 2.1 et 2.2. Les codes H'O', H'l', H'2', H'3' permettent de modifier séparément les bits du mot de contrôle concernant le spot. Les codes H'5', H'6', H'7', H'D', H'E' permettent de remettre à zéro les registres X,Y, ensemble ou séparément. Les codes H'4', H'6', H'7', H'C' effacent l'écran. Le code H'7' réinitialise en outre le circuit en remettant à zéro les registres: Contrôle, |\Delta X|, |\Delta Y|, et en positionnant à "un" les registres taillexcar et taillexcar.

Le mode d'accès aux registres a été choisi pour pouvoir accéder à tout ce qui définit l'état de la visu. Cela permet d'avoir plusieurs programmes fonctionnant à des niveaux d'interruption différents,

chaque changement de niveau étant associé à une sauvegarde ou une restauration des registres du circuit.

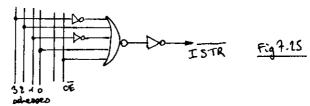

La case mémoire d'adresse H'A' a pour seul effet de générer une réplique de  $\overline{\text{MPCE}}$  sur la broche  $\overline{\text{ISTR}}$  (quelquesoit le niveau de  $\overline{\text{MR/W}}$ ). Son intérêt est de minimiser la circuiterie externe si on a besoin d'un registre supplémentaire (registre de couleur, ou registre de lecture sur  $\overline{\text{LSTR}}$ ). La sortie  $\overline{\text{ISTR}}$  peut être utilisée uniquement en lecture, ou uniquement en écriture ou dans les 2 sens. Deux exemples d'utilisation sont donnés en Fig.2.29 et 2.30. Dans le deuxième exemple, il est entendu que le programmeur n'utilise cette adresse qu'en lecture. Pour plus de sécurité, on peut ajouter la condition  $\overline{\text{MR/W}}$  sur la commande de lecture du registre.

Utilisation de la sortie ISTR en écriture pour échantillonner un registre de couleur dans une application 256x256points 8 couleurs.

Utilisation de la sortie ISTR en lecture pour positionner sur le bus microprocesseur la valeur lue après l'utilisation de LSTR.

Remarque: on sait à quel moment la lecture a été effectuée par la

surveillance du signal "libre" (bits 2 et 6 du mot d'état).

# 2.18-RECAPITULATION DES CODES

|                 |          | l               |                                                                             |                                                         |

|-----------------|----------|-----------------|-----------------------------------------------------------------------------|---------------------------------------------------------|

| Adresses        | WE       | Eciture         | Lecture                                                                     |                                                         |

|                 | <u> </u> | Commande        | Not d'elfat                                                                 | <del>-</del>                                            |

|                 | 1        | Contrôle        | Contrôle                                                                    | _                                                       |

|                 | 2        | IX XI           | IAXI                                                                        | _                                                       |

|                 | _3       | IDYI            | IVAI                                                                        | _                                                       |

|                 | 4        | X haut          | Xhant                                                                       | _                                                       |

|                 | <b>S</b> | Xbas            | X bas                                                                       |                                                         |

|                 | 6        | Yhant           | Yhant                                                                       | <del>-</del><br>-                                       |

|                 | 7        | Ylvas           | Ylas                                                                        | _                                                       |

|                 | 8        | taille X can    | boulle xcan                                                                 | Light pen non lu                                        |

|                 | a        | KoulleYcan      | Paille Y can                                                                | - 47.11                                                 |

|                 | Α        | Registe externe | Registre extorne                                                            | X highly pen                                            |

|                 | В        |                 | X Light per                                                                 | → <u> </u>                                              |

|                 | C        |                 | Y hight pen                                                                 | Disposition du registre<br>Xlight pen sur le lus        |

| Mot de contrôle | 7 6      | 34              | Allumé/Erent<br>laquant/Effaçan<br>laquant/Effaçan<br>laqua d'IT { Fû<br>Eû | (contôle la sortie IWEN)<br>L' (contôle la sortie IDIN) |

| Met d'état      | 7 6      | 1 1 1 1         | . L.P. termine' Für tame Eviture libre Spot howde la fe                     | nête                                                    |

Tableau 2.1

| 4 4 4 4 4 4 4 4 4 4 9 9 9 9 9 9 9 9 9 9 | 8 3 A B C D E F |                                                         | All lays Direction of Shapes |       |      |           |         |         |       |         |             |        |              |          |        |       |                     |

|-----------------------------------------|-----------------|---------------------------------------------------------|------------------------------|-------|------|-----------|---------|---------|-------|---------|-------------|--------|--------------|----------|--------|-------|---------------------|

| 0 T T                                   | 4               | +                                                       | 5                            | ب     | ٩    | ىد        | 4       | 5       | ş     | ×       | dr.         | ×      | ~            |          | 3      | 5     | Nop                 |

| 0 7 7 0                                 | 9               | ,                                                       | 9                            | ರ     | ય    | -4        | J       | 90      | مو    | 4       | · · · · ·   | ż      | শ্ব          | 8        | *      | ¥     | Ь                   |

| 0 4 0 4                                 | 5               | J                                                       | Ø                            | 4     | S    | <b> -</b> | Þ       | >       | 3     | ×       | <b>&gt;</b> | 2      | L            | /        | Γ,     | 4-    | ↓                   |

| 0 4 0 0                                 | 4               | @                                                       | А                            | 8     | U    | Α         | ш       | U       | Ų     | π       | 1           | b      | ¥            |          | Σ      | Z     | 0                   |

| 00 4                                    | 3               | 0                                                       | ~⁺                           | 7     | 3    | 4         | S       | 9       | t     | ∞       | عا<br>و     | ••     | ••           | <b>~</b> | 11     | ^     | i                   |

| 0040                                    | 2               | Spring                                                  |                              | =     | #    | ₩         | %       | ⊗       | ,     | )       | (           | *      | +            | ,        | ı      | •     | /                   |

| 007                                     | 7               | Verbeurs de diractions<br>printégrées Tragages Verbeurs |                              |       |      |           |         |         | ^     |         |             |        |              |          |        |       |                     |

| 000                                     | 0               | Mode<br>Hong E                                          | Mode<br>Effet                | Spark | Sat  | Effar!    | (m.r. = | Pooti & | Reint | Ace. E. | f.e Ein Re  | Sx7    | Parel<br>Ux4 | food     | ClearX | Chany | Lectral<br>position |

| 4                                       |                 | 0                                                       | 7                            | 2     | 3    | 4         | S       | 9       | 7     | 80      | 6           | ٨      | 8            | J        | Α      | w     | LL                  |

| , "/                                    | 0               | 0 0                                                     | ¥ 0                          | 70    | イヤ   | 9         | ۲۰<br>0 | 0<br>7  | オヤ    | 0       | 40          | 0<br>7 | マヤ           | 0        | 40     | 0     | ヤヤ                  |

| 4                                       | 3 2             | 00                                                      | 0 0                          | 00    | . 00 | 40        | 40      | FO      | 40    | 0 7     | 0<br>4      | 40     | 7 0          | マヤ       | ヤヤ     | 4 4   | マヤ                  |

Tollean 2.2

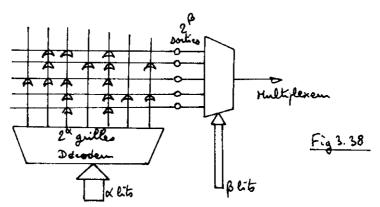

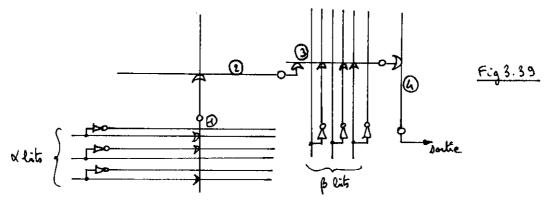

## 3-METHODE D'IMPLANTATION

- 3.1-Introduction.

- 3.2-Méthode utilisée.

- 3.3-Contraintes conduisant à la structure des briques.

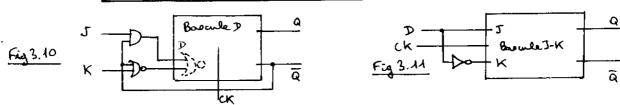

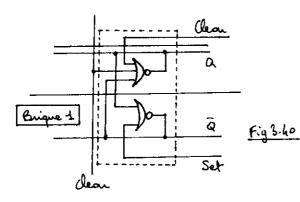

- 3.4-Structure des bascules.

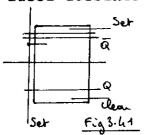

- a)Bascule R/S.

- b)Latch.

- c)Bascules non transparentes.

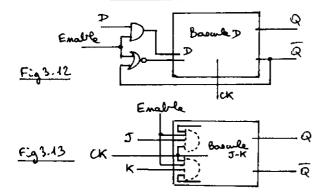

- d)Adaptation des entrées des bascules.

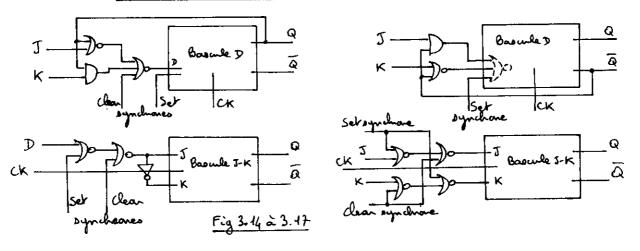

- i)Entrée J-K sur une bascule D et vice-versa.

- ii)Entrée Enable.

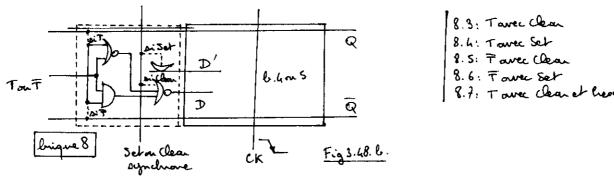

- iii)Bascule avec Clear ou Set synchrone et entrée D ou J-K.

- e)Conclusion.

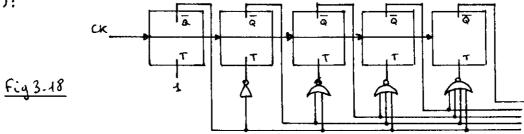

- 3.5-Structure des compteurs.

- a)Report de compteur UP.

- b)Report de compteur UP/DOWN.

- c)Reports d'entrée et de sortie.

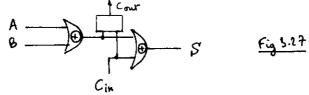

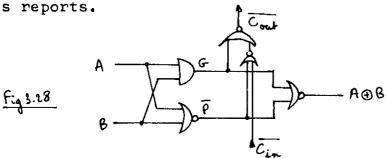

- 3.6-Choix d'une structure d'additionneur.

- a)Introduction.

- b)Propagation du report en une couche logique.

- c)Identité des étages pairs et impairs.

- 3.7-Comparateurs.

- 3.8-Mémoire morte.

- 3.9-Récapitulation: Bibliothèque de briques.

- a)Bascule R/S.

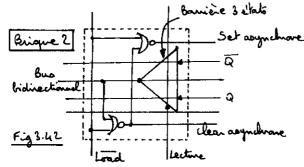

- b)Load asynchrone et sortie 3 états.

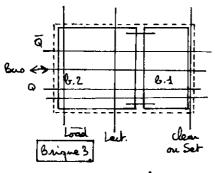

- c)Latch à sortie 3 états et Clear ou Set.

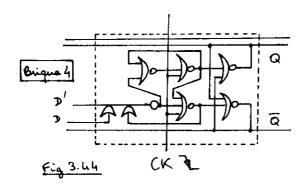

- d)Bascule D-D'.

- e)Bascule D avec Clear et Set asynchrones.

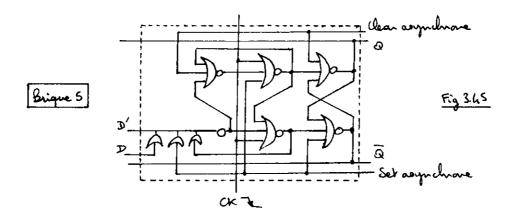

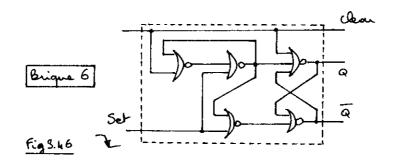

- f)Bascule à Set sur front et Clear asynchrone.

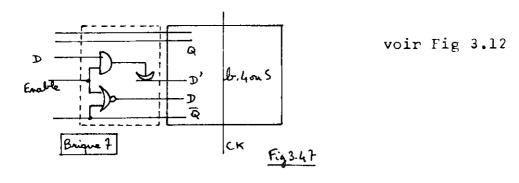

- g)Bascule D avec Enable.

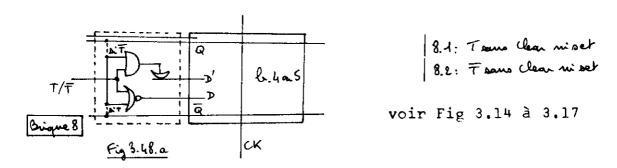

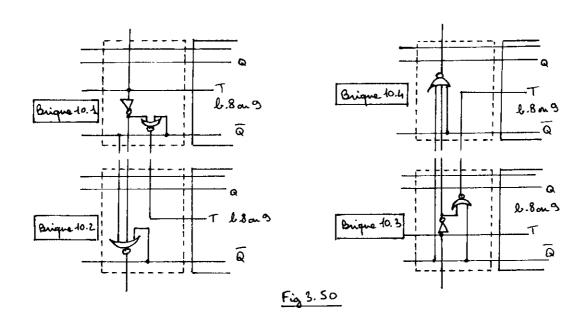

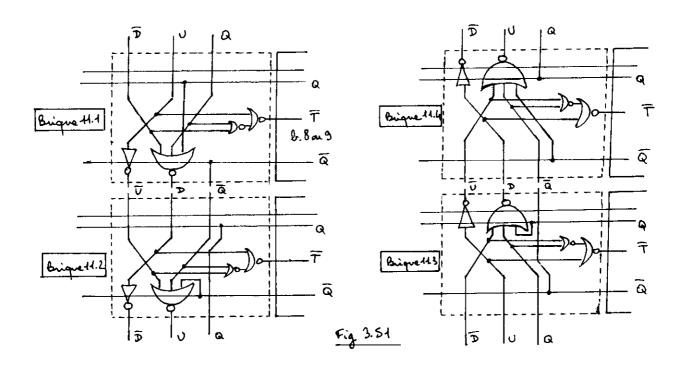

- h)Bascule T ou T avec Clear ou/et Set synchrone.

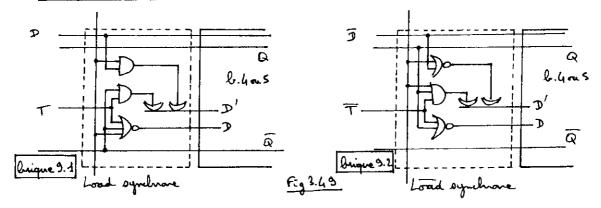

- i)Bascule T ou  $\overline{T}$  avec Load synchrone.

- j)Report de compteur UP.

- k)Report de compteur UP/DOWN.

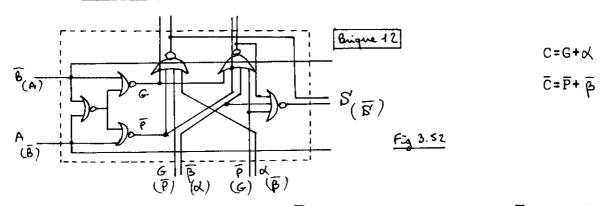

- 1)Additionneur.

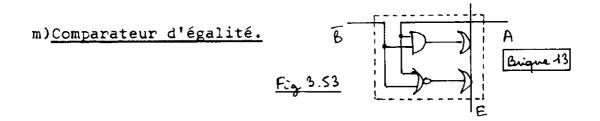

- m)Comparateur d'égalité.

- 3.10-Plan des chapitres suivants.

#### 3.1-INTRODUCTION

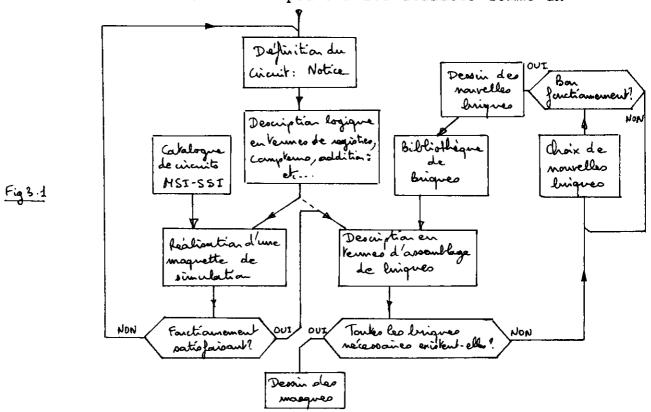

Le chapitre 2 décrit le circuit intégré graphique en tant que "boîte noire", dans le langage des utilisateurs: concepteurs de consoles et programmeurs. Il faut maintenant passer à une description détaillée en vue de la réalisation physique du circuit. C'est le dessin des "masques"; toutes les étapes ultérieures de la réalisation (découpage du stabilène, réduction à l'échelle, photorépétition et traitement chimique) sont pratiquement automatisées, et en tous cas ne font pas partie de la conception proprement dite.

Le passage de la description fonctionnelle du circuit au plan des masques peut se comparer à la suite: compilation, édition de liens, et chargement pour l'exécution d'un programme écrit en langage évolué. Mais dans notre cas, aucune de ces étapes n'est automatisée, et ce travail demande plusieurs mois.

Pour des circuits d'une faible complexité (quelques centaines de transistors), ou pour ceux dont le taux de répétitivité est élevé,

on peut commencer par la mise au point d'un schéma électrique décrivant le circuit au niveau des transistors et des connexions. Le fonctionnement est alors testé à l'aide de "simulateurs électriques", programmes appliquant les lois de KIRCHHOFF pour ce réseau.

Mais la complexité atteinte aujourd'hui couramment pour les circuits commercialisés est 10.000 transistors (100.000 pour des circuits hautement répétitifs tels que les mémoires). Or, tous les circuits de cette complexité qu'il serait intéressant d'intégrer ne sont pas forcément répétitifs!! On peut toujours dégager de petits sous-ensembles qui le sont, mais il faut une fonction vraiment spéciale pour que tout le circuit le soit.

Passer directement au dessin des masques est impossible car cela demande la manipulation d'une quantité d'information gigantesque. D'autant plus que, la correction des erreurs ne pouvant alors s' effectuer qu'après la réalisation physique du circuit, ce travail est comparable à l'écriture en binaire d'un programme de 100000 instructions dont le chargement avant exécution pour test prendraient 6 mois à chaque fois.

Or, l'automatisation de ce travail est beaucoup plus compliquée que l'écriture d'un compilateur pour un langage de haut niveau. En effet, ce "compilateur" devrait manipuler une information qui n' apparaît pas dans le langage source: les connexions. Pour un programme, toutes les références à une variable sont identiques car on part du principe que le temps d'accès à toutes les cases de la mémoire est identique. Mais dans le dessin des masques d'un circuit, une connexion dépend de la localisation des variables. Elle occupe une certaine surface comme un opérateur, et pose des problèmes de topologie [3]. Le "compilateur" doit donc créer ces nouveaux éléments dont la manipulation est souvent plus délicate que celle des

opérateurs décrits dans le langage source. Pour ces raisons, de tels compilateurs n'existent pas encore, et ce travail doit se faire manuellement.

La mise au point de la méthode a donc une importance capitale. En particulier, il est indispensable de pouvoir valider la logique dans une des toutes premières étapes (ce qui est équivalent à la "preuve" d'un programme écrit dans un langage de haut niveau). De plus, la chaîne de transformation entre cette étape validée et le dessin final doit elle-même être prouvée. Ce n'est qu'à ces conditions que l'on peut être sûr que des mois de travail ne seront pas à recommencer.

### 3.2-METHODE UTILISEE

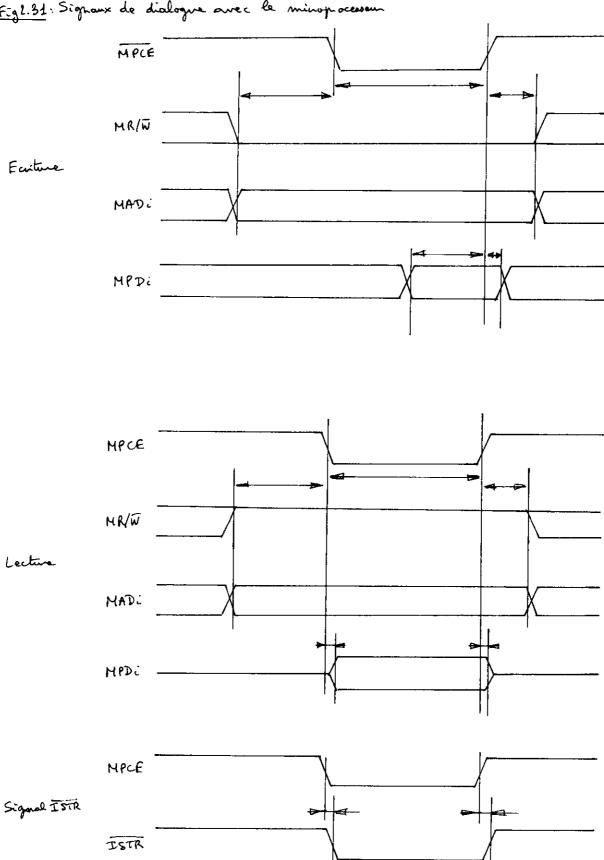

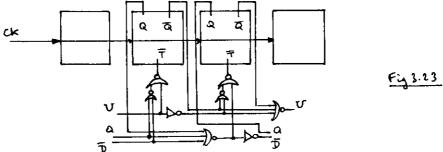

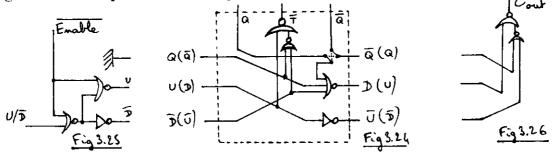

Nous avons choisi de progresser dans la définition du circuit de la façon suivante (inspirée du chemin utilisé par J.GASTINEL pour le dessin du circuit SFF 96364 [8]): (voir Fig.3.1)

<u>lère étape</u>: Description de la logique du circuit en termes d'opérateurs évolués tels que registres, compteurs, additionneurs, multiplexeurs, etc... A ce niveau, ces éléments sont indépendants de la technologie de réalisation. On parlera par exemple d'un "Compteur UP, n bits, synchrone, avec Load asynchrone".

<u>2ème étape</u>: On traduit cette description en un plan de câblage dans une technologie correspondant à des délais de réalisation les plus courts possibles. Aujourd'hui, ce sera une maquette à base de circuits MSI et SSI (dont le câblage et la mise au point peuvent prendre moins d'un mois). Ceci apporte une simulation logique en temps réel qui permet une validation très précoce, et permet de plus de travailler parallèlement sur les applications du circuit, ce qui en général rejaillit sur sa définition extérieure. Les allers-retours

notice-simulation sont rapides et court-circuitent toutes les étapes longues d'implantation.

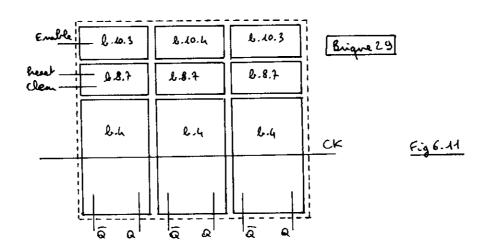

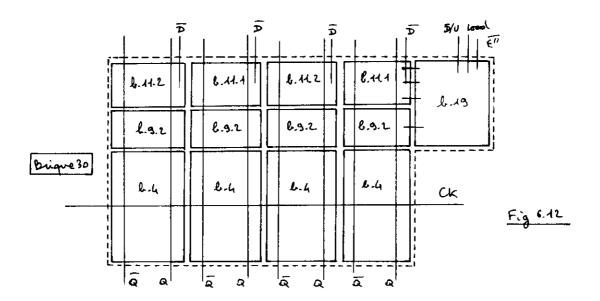

<u>3ème étape</u>: On traduit la description de la première étape en un assemblage de briques dont le fonctionnement est prouvé et dont le dessin existe déjà. Il ne s'agit pas simplement de briques dont la forme est prévue pour un assemblage simple, mais elle doivent être conçues de telle manière que leur utilisation soit indépendante de leur structure interne. On doit pouvoir les utiliser comme un

programmeur utilise des sous-programmes d'une bibliothèque standard. En particulier, ces sous-programmes ne doivent pas modifier des variables globales qui ne sont pas passées en paramètres. La fonction de ces briques doit pouvoir se définir par une relation booléenne liant les sorties aux entrées, modulo des considérations d'"entrance" et de "sortance" électriques. Ce n'est qu'à ce prix que la notion de brique simplifie la description des masques.

<u>4ème étape:</u> Le travail d'implantation du circuit se ramène alors à la définition des briques qui manquent à la bibliothèque, suivie de

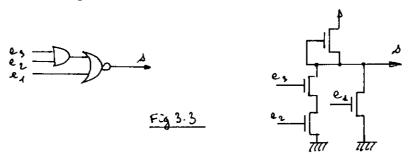

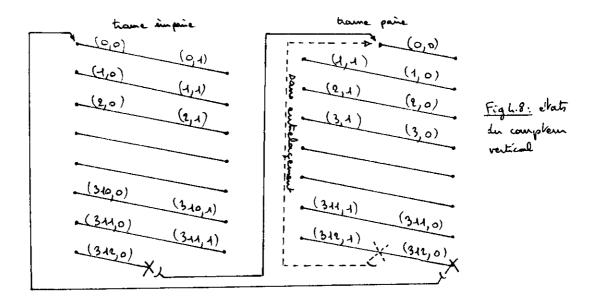

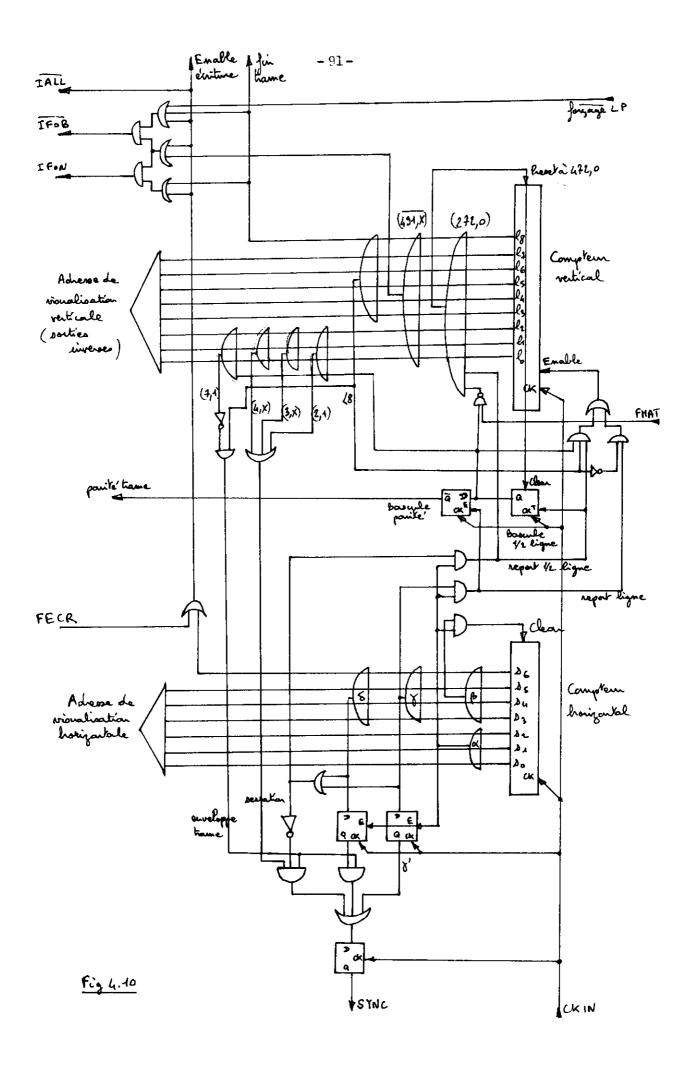

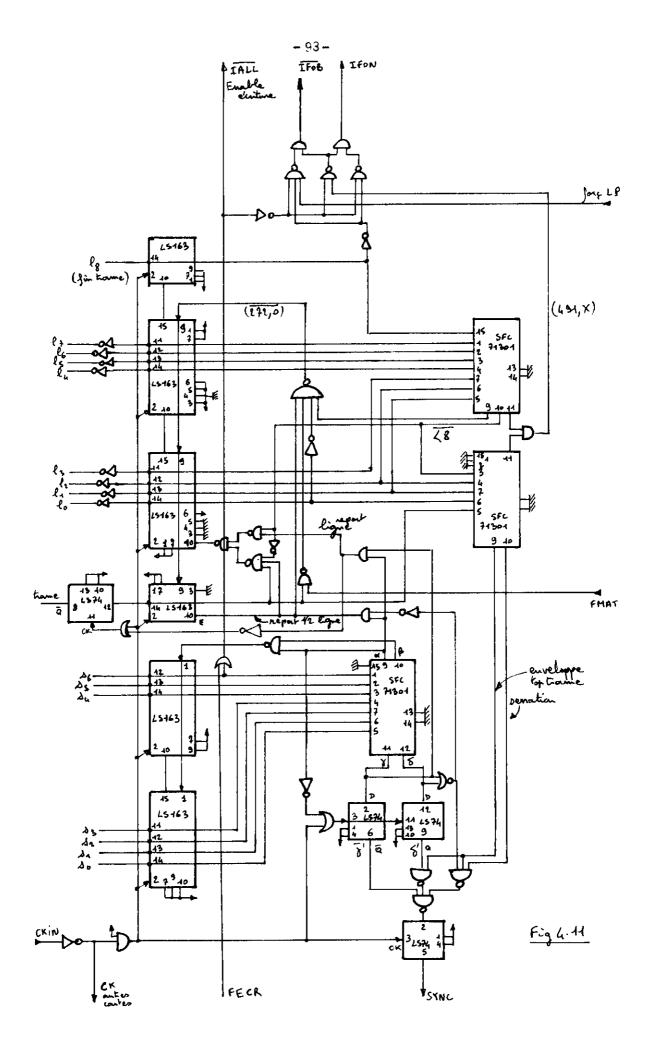

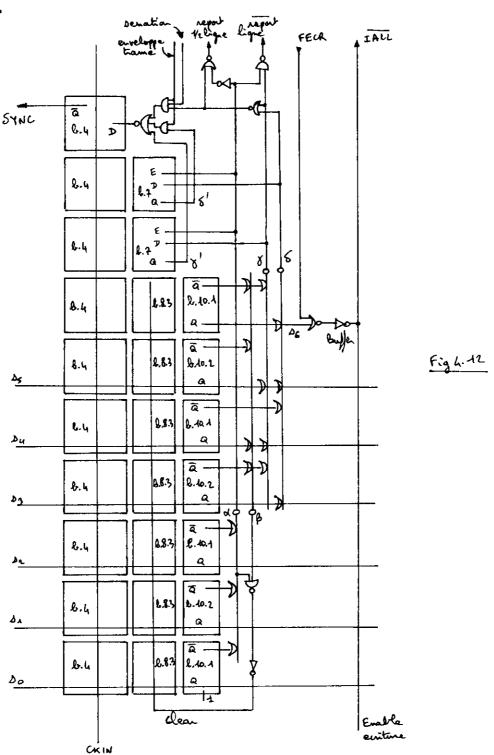

leurs dessins et de leurs preuves.